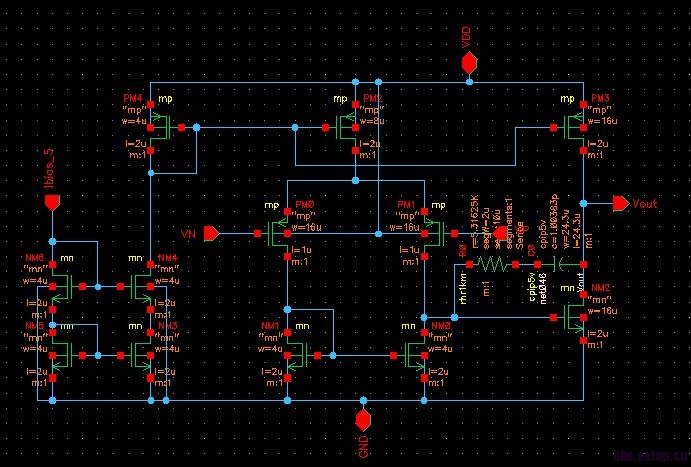

求高手指教!关于运放的电源电压抑制比问题!

PSRR左端是运放增益撑着,右端是靠的输出管子等效电阻相关的gds及cgs,cgd及负载电容的RC网络决定的。改改第二级。负载要带上的啊。

http://bbs.eetop.cn/thread-323176-1-1.html

旁边这个帖子有模型。看看吧

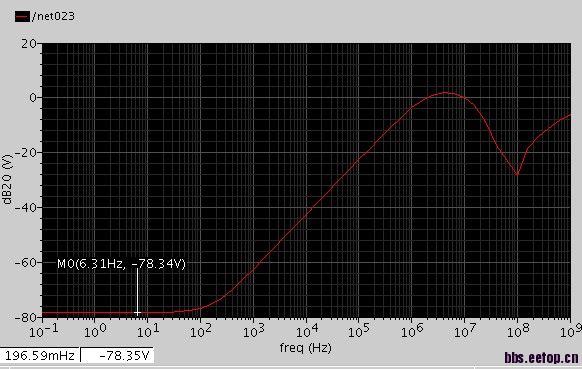

谢谢!不好意思啊,可能我的表述出问题了,我的真实意思是抑制比这条线上升得太快了,到1MHz的时候已经很小了。不是指高频端太小,我只想在1MHz的时候也能有比较大的抑制比,再高的平率就无所谓了。

那条曲线是增益的下降曲线,20dB/频程。不可能改好。

你唯一可以考虑的是把右边的PSRR做好,让左边和右边的PSRR高的区域尽量重合。

恩,谢谢!我再改改。

把差分对的Bulk接到源极呗。

推大-3DB带宽,同时尽量保持高增益,很难,不过你这个还能提高

提高差分对管的电流,增加单位增益带宽,准行﹣如果不可惜功耗的话。

想办法增大带宽。不过,1M处的不通过加RC滤波是很难有很高的psrr的。

你这个电路,改进的空间很大哇

换成cascode miller补偿

在PM4的栅极到VDD加一退耦电容试试。

有一个很不好的方法就是增大带宽,减小米勒电容,当我没说!

求教,哪些地方可以改进,非常感谢!

这种miller compensation的PSRR的传输函数的主极点同differential gain的传输函数主极点相同,就出现了20db的degradation。如果输入级结构不想变得话,可以用ctive compensation技术试试,psrr的主极点会高一些

就是 cascode miller 补偿

麻烦问一下,这个电源电压抑制比用的是输出电压的变化量比上电源电压变化量呢,还是反过来的!是越高越好,还是越低越好!

PSRR is the ratio of output voltage change to power supply voltage change.当然越小越好啦

try to enlarge the bandwidth,

是不是那个补偿电容可以考虑一下换另一种结构