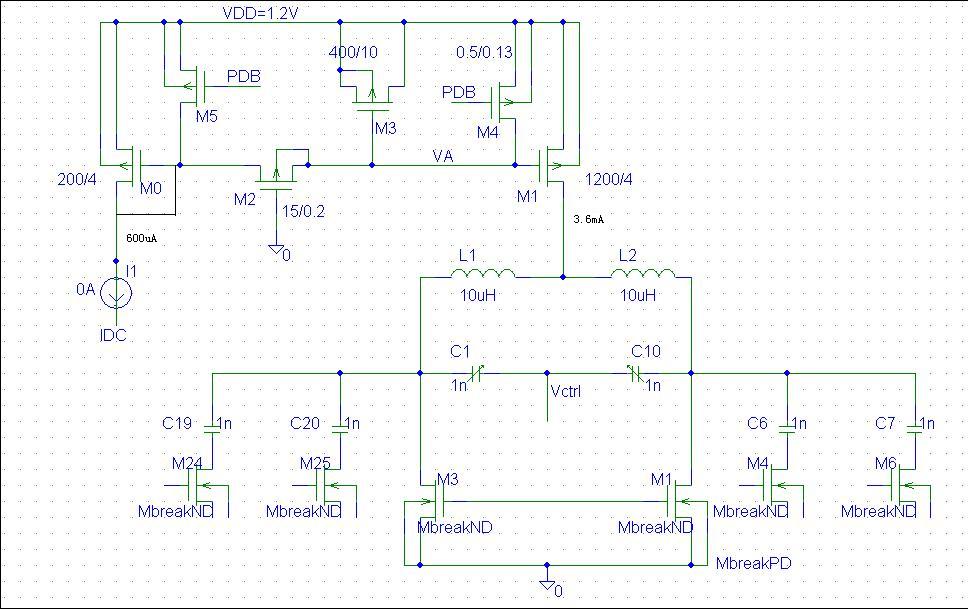

VCO偏置漏电流问题

但流片后测试时,镜像电流源电流少了30%以上,同时测得电流源栅极处的电压是550mV(Vgs减少,电流源电流当然减少),现在基本上可以判定这个做电阻的pmos管有压降,即Vds达100mV左右,那么这个pmos res管(M2)也应该有不小的电流了(100mV/2M=50nA)。但问题是该管D,S串在镜像电流源的栅极上,其电流从何而来?

另外,M4,5是powerdown管,0.5/0.13.

好帖,希望有高手来顶

M0应该结成diode形式。

M2的bulk应该接到Vdd,

LC tank里面的两个NMOS应该有bias的,在哪里?

不知道你怎么测得?M2上没有压降是因为接gate的缘故,但是测试设备(比如万用表)会引入一个测试点到地的阻抗,所以这时候测试结果不一定准确,所以你怎么就能判断电流的差别是M2引起的?有可能你本身偏置电流就偏差很大呢?

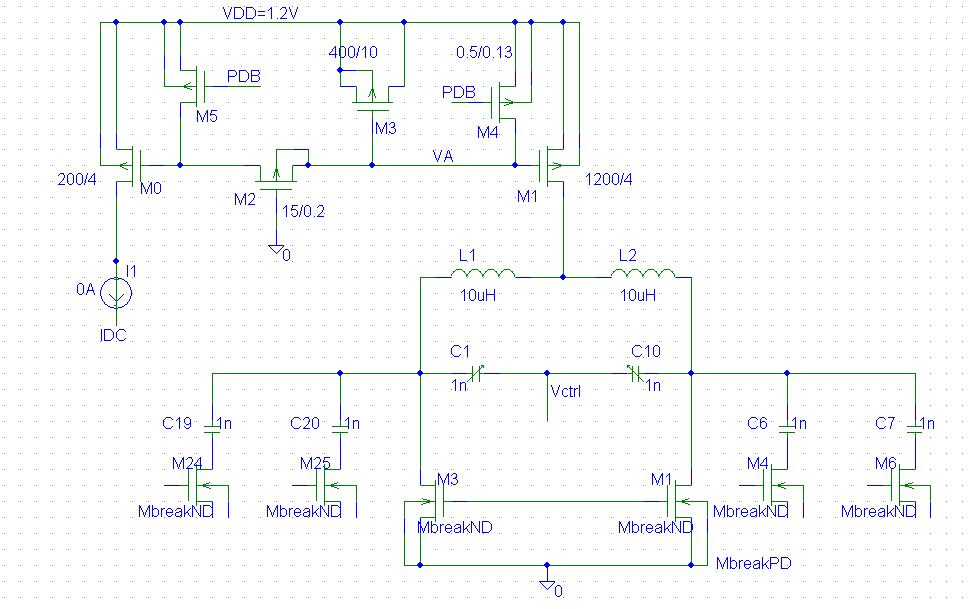

PS:你的电路图不对,不知道是不是遗漏了

这个数据是如何得到的?

M2可能工作在weak inversion区域,需要很长的启动时间

[8800*16pF/um2]*0.6V/50nA=1.7s

这个电路按说电流应该小掉100%

电路图是错的

不好意思,各位。

由于疏忽,电流镜中的M0管是画错了,但设计时是没这个错误的,都是连接好的,并仿真无误。

我将M2的B、S连在一起当时是为了减小Vth,以免出现的较大的Vdc。流片后,我再VDD处断开串入万用表测电流,电流的确少了30%,而在VA处我之前留了一个pin,用外用表测其电压,比仿真的高100mV。整个测试过程应该没大的误差,VA电压升高,VCOCORE电流减少,也导致变容管的电位变化,频率升高10%,这和我后来在仿真时改变VA的电压所得到的频率是很接近的。

还是请大家帮我看看M2的电流(40-50nA)从何而来?是不是M1管面积太大,衬底产生漏电流?还是powerdown管的漏电流?很困惑!

将正确的图补上!

谢谢大家!

请教一个问题:

m2其栅极接地,该pmos工作在深三极管区。为什么栅级接地,它就工作在深三极管区了?工作在深三极管区的条件是vDS<<2(Vgs-Vth)

你的pmos用作深三极管区电阻的长宽比是不是弄反了?应该L很大,W小才对哦。

表示没有看懂

个人认为是那只做电容的pmos搞的鬼,0.13栅极漏电很大,但是弱国model没有做这个,仿真放不出来

不过小编的证据不是很充分,因为vgs偏小有可能是管子偏corner,与漏电没关系