SD DAC请教

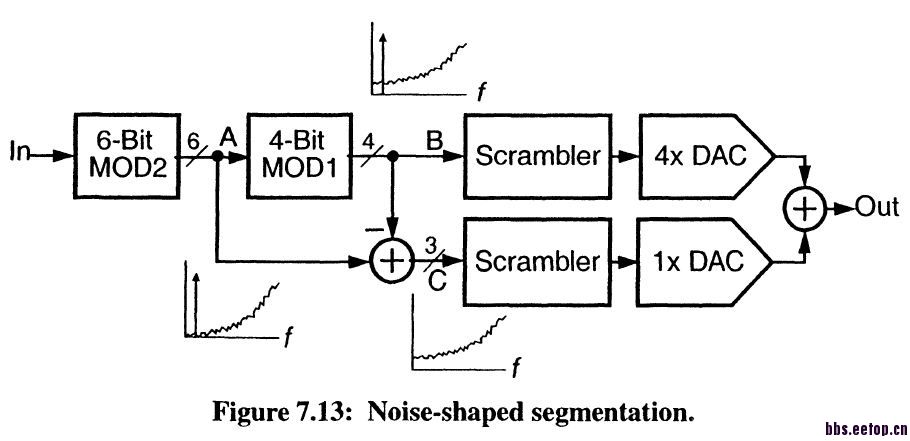

请问这个C为什么是3bit的数据呢?这个是怎么换算的呢?

请各位赐教谢谢

不要沉了,自己顶一个,各位指点一下咯

以MOD2(6bit, binary code)來看假設把全部SDM 輸出範圍變成 64 level, 假設最小一格的單位是1

以MOD1(4bit, binary code)來看假設把全部SDM 輸出範圍變成 16 level, 因此最小一格的單位是4(以MOD2的1格輸出為單位) 在C節點 C=A-B => 輸出數值 4(A node)-(1,2,3,4,B node)=0,1,2,3

因此C節點應該是thermometer code 3 bit

感谢楼楼上的解答

在C点,因为是thermometer code,所以才是3bit,而按照binary code来计算的话,这个地方就是0,1, 2, 3四个level,也就是binary code的2bit数据,是吧?

LS是不是uestc的?

A点 和 B 点 相减时 是把 B点的 4位数据前面 补0 么 ?。从A经过MOD2后 数据变短是 怎么 截断的啊?。

你真的要做sigma delta DAC 不要用這種架構 用單一quantizer 的迴路就好了 這是paper 搞學術創新 實際上可用程度很低

这个好像是ADI的paper. ADI 的东西大部分都是用来量产的

建議初學者採用單quantizer架構 每種架構數學上都可以互換 所以數學上是等價的 只是你要設計NTF 如果是SD DAC你也用error feed back架構 很直覺很簡單 數學堆導一下即可 後面加1st/2nd order DEM for capaciror mismatch, SC DAC with 1st order lowpass & active-RC low pass filter (2nd order)

建議多看ADI 與cirrus logic的paper

这个经过以后相当于两个数据的权重不一样,相减的时候,要做补零

之前的架构用的是单一quanatizer的结构,现在性能要求高了,所以老大说尝试这种结构,也看到ADI的一篇文章

所以想评估一下。

你原來架構出來的數位SNR 跟後面量到的類比SNR 各是多少? 如果落差大就是類比的問題

數位端拉高OSR也可以啊

thanks a lot, i am very interested in adc design, do you know where can we find ADI adc papers? all i can find is data sheet.

这个价构是可以用的。现在的DAC如果还用1bit量化的话噪声太大,后面的滤波器不好设计。这种多bit的架构很实用,建议采用。据我所知ADI有产品用这个架构,国内有公司购买该IP。

I saw the ADI paper in IEEE JSSC.But that was several years ago.

现在我们是限于面积以及噪声的的要求,因此想换成更多bit的结构,来优化其带外噪声

也是看了ADI相关的paper才决定选取这种结构

Multi-bits 比較好 信號DR比較大 modulator 穩定性也比較好設計 analog post filter 規格也會比較鬆 比較好設計