比较器中一个powedown管的作用

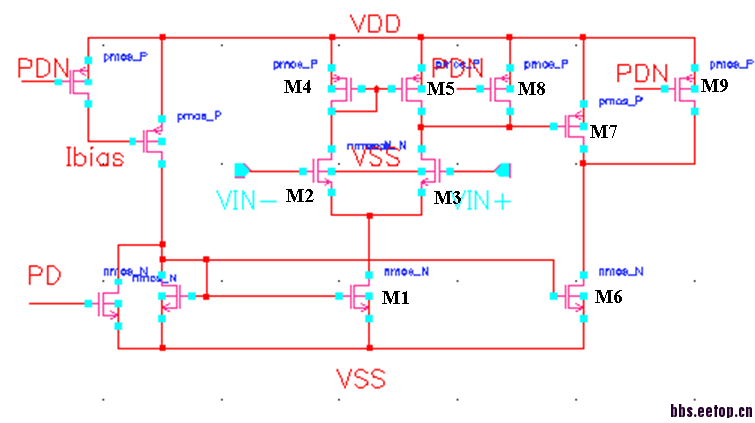

有如下比较器电路

它是间歇式工作的,比较一次后,powerdown一段时间,再开启。

PD与PDN是相反的信号,我认为M8管似乎是多余的,请大家帮我看看,M8有什么作用?

没图没真相!

已附图,请指教。

power down的时候,M5漏端是个高阻节点,电压不定。M8的作用就是把这点的电压给固定下来。

~个人见解,欢迎赐教!

有道理!谢谢!

但是,高阻节点,电压不定会带来什么影响?

这个就不大好说了,我也问过一些人,他们给出的答案更像是一种习惯,不希望电路里出现自己不能确定的东西;我觉得可以考虑的因素有很多,比如说管子的意外导通,管子的使用寿命等等;如果有大牛能透彻地讲解一遍那就最好了!

谢谢!你的回答很不错了!

也期待有讲得更透的高手!

首先要确认恢复回来的时候初始状态是什么样子的。如果M8不加,那么M7的gate状态不定。如果pmos漏电大且时间够长,那么M7必然拉高。如果在你关掉之前M7gate是低,并且漏电不大,且时间很短,但是你初始状态需要M7为高,那你又怎么办?这个和你电路绝对有很大的关系,和工艺关系也很大。供参考。

沒錯 M8是多餘的 power down 時 輸出會被M9 pullhigh M8有沒有都不重要 但是M8應該用minimum size面積很小 成本應該沒差 只是加了M8在你模擬時M7的gate端會有確定的狀態 如此而已

如果电路出了bug的话,知道电路里每个节点电压的确定状态,这样debug比较容易

可能就是随手加的,可以去掉

最好加一下M8 因為如果處於power down 狀態而無M8 M7 的gate會變為 floating 很容易受干擾 這時如果附近有clock 線 couple 到M7 讓M7 不穩定形成通道 解除通道(|Vgs|>Vth, or |Vgs|<Vth) NWELL 裡面會有很多載子在M7 gate(M7 應該滿大顆)下面 跑來跑去 會形成一個雜訊源 造成NWELL電位不穩 所以共用此NEWLL之PMOS都會受到干擾尤其是直接連到 power 所以此power線上會有很多雜訊 因此還是加M8比較好反正M8都是用minimum size 沒差 加上M8會保證M7一定在cut-off region 最安全

你的回答很详细,谢谢,M7初始状态需要为高,你的意思是M7的栅为高,还是M7的漏为高?

不管需要M7的栅是什么电平,Powerdown以后,M7的漏都会被M9拉为高。

这确实也是应该考虑的问题。

我认为加了这个管子是有好处的,这样每次比较之前的状态都是一致的。其实在另外一条腿上面最好也加上一个,这样在比较之前两边的环境完全对称,对于消除一些记忆效应是有帮助的。

因为在你shutdowen这个block的时候并不知道之前的状态,如果你的leakage不大并且关断时间不够长,那你的M7的gate就会保持之前的状态,你能保证之前它是高吗?所以为了make sure,你必须要在shutdown的时候强制拉高,相当于给一个initial的状态。

很有道理

但考虑到M7的Nwell在layout里是默认连到VDD的,因此,Nwell似乎不会受M7栅压的影响。

其實NEWLL阻抗很高 如果M7 的gate端是高阻抗點 如果M7的gate又被couple noise 造成 M7開開關關 這時M7的 channel 會形成與消失 carrier 會在NWELL內亂竄 造成NWELL 接近M7的部分 NEWLL電位不穩定 雖然你layout有打bulk contact 讓NEWLL 維持在VDD 但是因為NEWLL阻抗很高 M7 所在的NWELL附近電位其實不一定是VDD 會一直跳動 這是雜訊源 如果你的NWELL M7 附近有PMOS 那這個PMOS就慘了 Vth會一直跳來跳去 Id也會跳來跳去 所以建議 M7的gate最好在power down時 透過M8接到VDD 反正M8很小 不佔什麼面積

朱先生,12楼,17楼正解,谢谢!另问,如果,M2,M3是热阱(hot well),加上M8会不会带来一些影响?