关于比较器迟滞的调节问题

时间:10-02

整理:3721RD

点击:

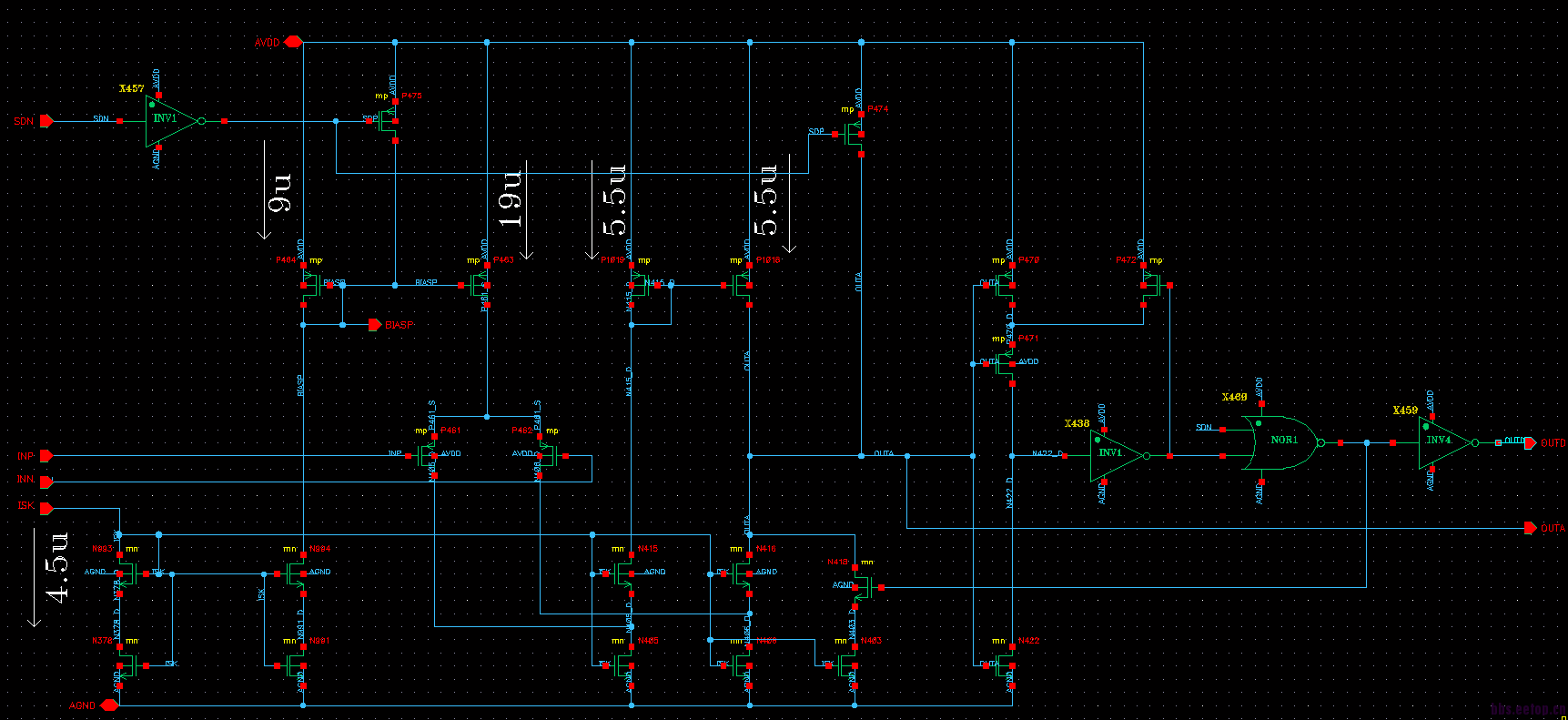

INP端为Vref=0.9V,INN范围为0--2V,2--0V. sim=dc, 目标迟滞电压为300mv-400mv,但是我调了两天了只能做到40mv迟滞,请教高人指点

图非常不清楚。迟滞就是输出结果会影响输入级系统失调,你把这个偏差调大就可以

点击贴子上的电路图就可以看清楚图片,高手请赐教,我的失调电压很小,仿真过。不胜感激!

你想要多少的迟滞?你这个迟滞干什么用?

目测你这个最下面的self cascode 的nmos是线性区的。不合理。

要求迟滞电压为大于300mV,用在环路补偿(EA的一部分),最下面的self_cascade作为负载,工作在线性区是没有问题的。

嗯,你的应用允许线性区就没事,就是增益低点。你这个难道是DCDC的EA,要做burst mode?若不是那为何用迟滞做在EA里面?

恩,是增益低点,设计它的是为了调节补偿电流,设计在EA中来做环路补偿!EA输出接Cap.

若环路补偿,电流模式可以在EA输出加电容。但我不明白你加迟滞跟补偿有什么关系,而且还有什么电流?

请赐教。

赐教不敢,从系统的角度,EA还有一个功能就是fast_start,此比较器有两个输出,一个是来控制充电,一个是用来送给PWM使芯片快速启动。不知道这么说能否理解。

哦,受教了,谢谢。有时间我看下这个电路的迟滞。

变NOR输出端控制的那路管子尺寸不管用吗?