CDR仿真结果的一点疑问

时间:10-02

整理:3721RD

点击:

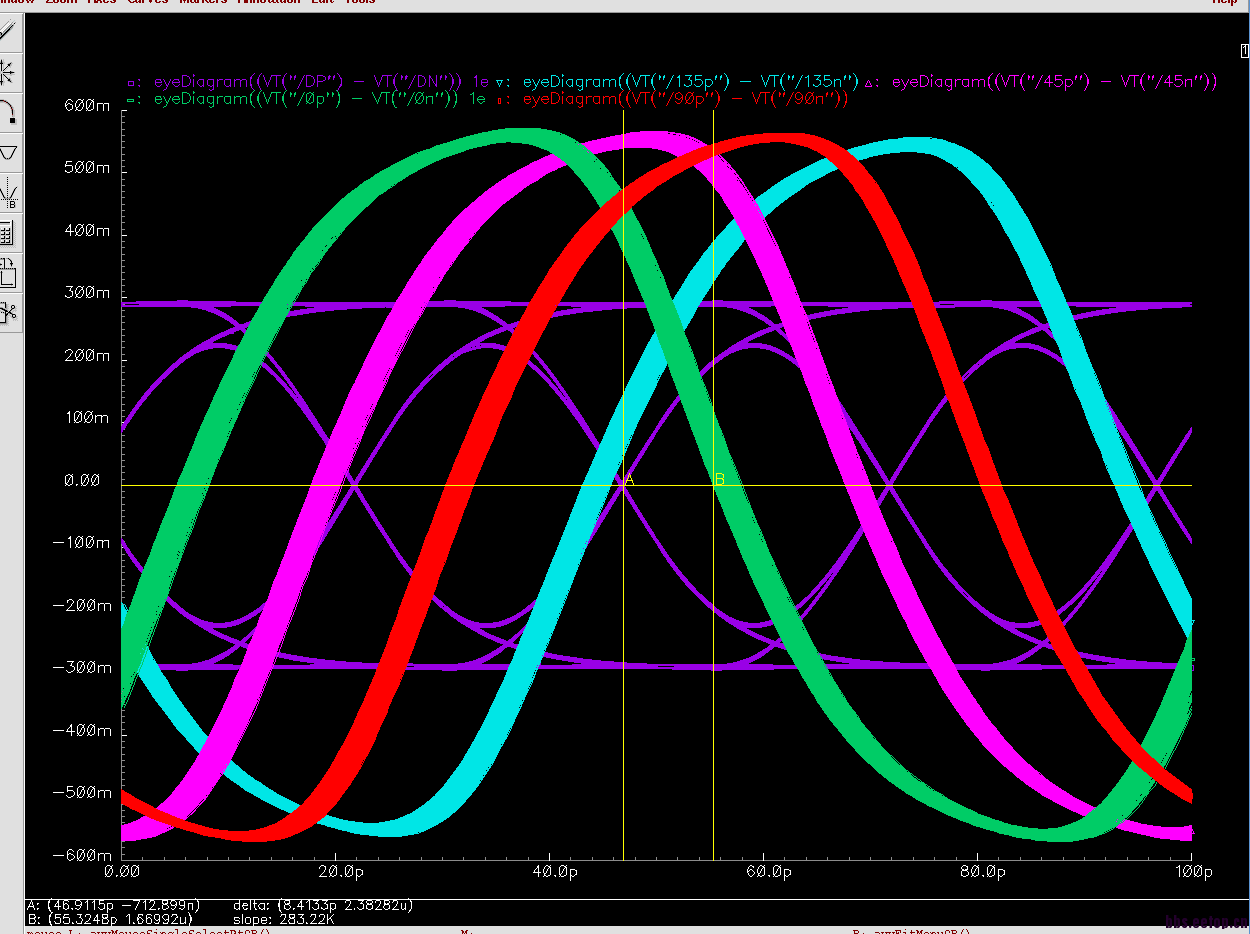

我做的CDR仿真有点疑问啊,就是数据和时钟存在频差的时候锁定时候没有锁定在中间,而是锁定在了一边,能容忍的频差为244ppm(是有点小,不过这个可以调的),图为-200ppm的锁定结果,+200ppm时会锁定在另一边,就不贴了。我查了查也没查出原因啊,因为PI的控制码是在有频差的时候一直增长或减小。

哪位知道是什么原因么。速度是40G,时钟是10G,四分之一结构

仿真精度是aps, conservative, 没有设置最大步长

哪位知道是什么原因么。速度是40G,时钟是10G,四分之一结构

仿真精度是aps, conservative, 没有设置最大步长

顶一下

求解答。是增益太小的缘故么