PMOS电容代替miller电容

求高人指点。

主次极点放错位置了

积累区?一般是耗尽区吧!

除非你用Nwell NMOS

什么叫主次极点放错位置?主极点是运放的第一级的输出决定的,次极点是运放第二级输出决定。还请指教。

你验证过么?

还有,你有调零电阻么?就是你的pmos电容串电阻了么。也可能是右半面零点的原因。

有调零电阻,在左半面。调零电阻对PM有一些作用。主要的是。我PMOS电容的尺寸增加,GBW增大。这点不解。

你的输出级是怎样的?

你的PMOS cap是怎么放置的,

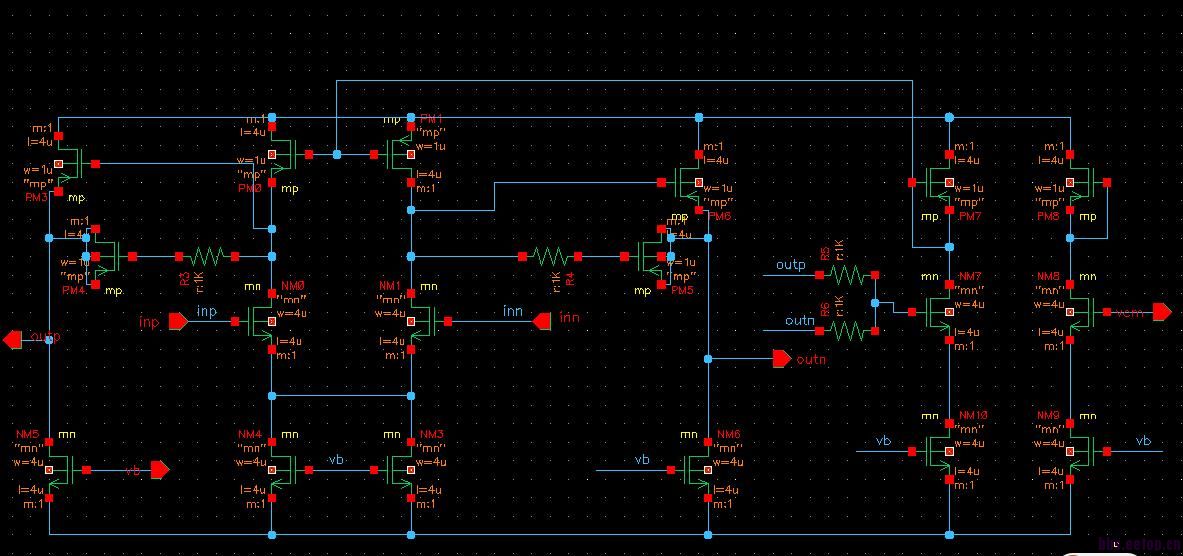

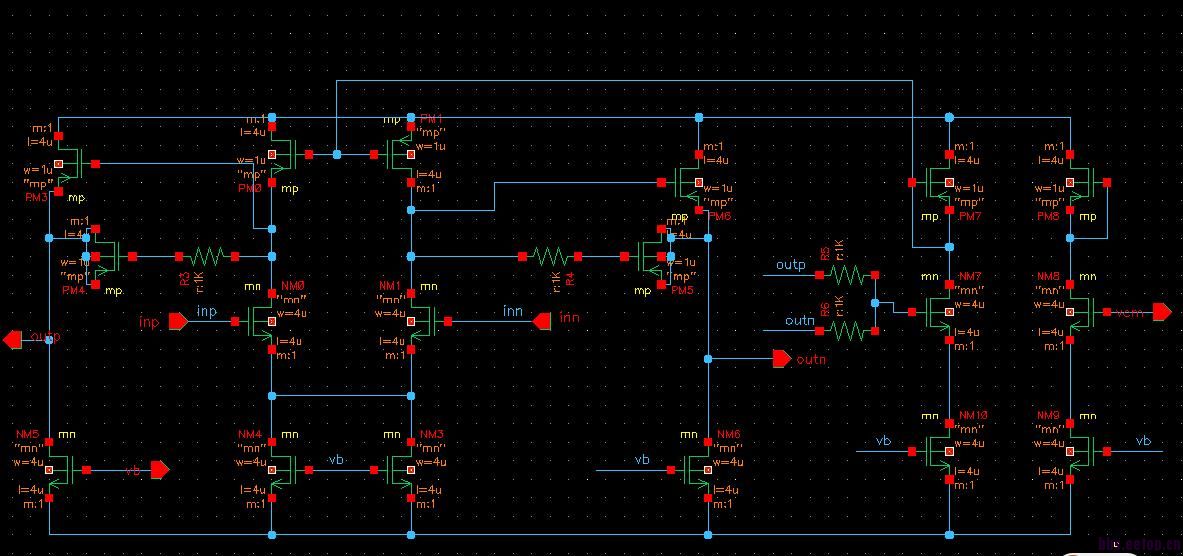

上图

感觉还是你的主次极点没在正确的位置

“我PMOS电容的尺寸增加,GBW增大”应该不太可能吧!除非主次极点对调了

电路如上图所示。pmos电容尺寸是60/10.电阻是4.9.该运放的负载电容是4.7P。请指教。

电阻4.9K

。smic 0.18工艺

smic0.18工艺

你的衬底都悬空,先都接上在仿真看看吧。

悬空仿真是不对的

衬底是接上的。因为公司的电脑只有内网,那个图是我用自己本子画的。就没接的。仿真了。

第一级和第二级电流分别是多少

第一级是80u.第二级是300u.共模支路是40u.....

What is your pmos body voltage? Is it as same as supply? If not, you are going to have difficulty in layout.

你这个是什么东西,那么费电啊。

电路的尺寸也是示意图把,不是你实际电路的尺寸。

不用贴图了,你极点位置肯定不对。你可以现那个理想电容代替pmos电容。搞好了在换成pmos搞。

it is as same as the supply.

seeing

我需要差不多400M的带宽。再请教下,MOS 电容的容值在属性里看不见,是不是需要进行DC仿真之后在print下的DC operating points看。

上面的尺寸不是实际电路的尺寸。可是我不理解主次极点颠倒,之前miller电容是用MIM电容的。60/30的尺寸。差不多1.7p..觉得尺寸大,才改成MOS电容。

建议你别用pmos电容,有native nmos可以用,没有就用mim电容。

可以简单介绍下,为什么么?谢谢了。

电容变化太大,

PIP,MIM Cap

1.不建议用pmos电容,确实变化太大(比nmos电容要大,看看器件可以知道),有可能你在没加大pmos管面积之前,工作在积累区,但加大面积后,有可能也会使栅电压变化(看你W/L是增大还是减小),这样有可能会进入亚阈值区域,这样电容可能还会减小,从而可能导致GB增大。纯属猜测。

2.在面积增大的情况下(Cc增大),大家都提到的两个极点位置反了怎么会导致GB增大?表示困惑?

可能进入了耗尽区,最后如果解决了希望能把结果公布下。