高频正弦波如何转换成方波

inverter

ac couple + self bias inverter + inverter

顶3楼的方法

CML+inv

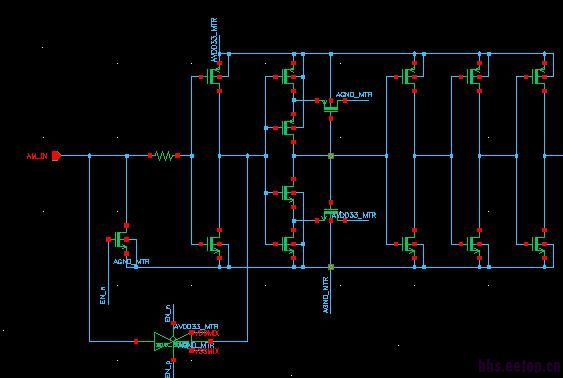

前辈,可不可以再详细讲一点啊?谢谢你的电路是使用在芯片内部的吧。是不是类似下面这种电路。还是其他。

这个方波我主要是用于ADC里面的。

但是那个之前设计的时候没有考虑到测试仪器的参数。不能产生400M的方波信号。

我想问问现在可以用板级的什么方法或芯片来补救。

单个反相器应该很难保证占空比偏差较少吧

CML在400M的频率会不会功耗很大啊?

烧多少电,关键看你对jitter的要求了

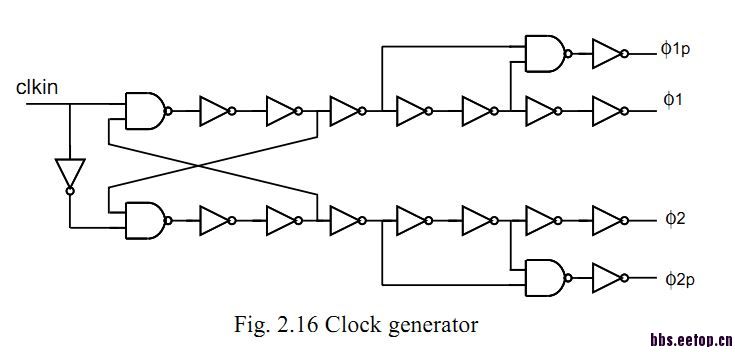

你的图是生成不交叠时钟的,跟你问的事情两码事

反向器的翻转电平只要和你正弦的共模一样为啥会占空比不一样?难道你时钟是片外给的?

原来是ADC clock... ,做之前没想好测试方案?

是用了GPIO跑不到400MHz?

你现在chip的clock input是单端的?I/O是standard I/O?

现在遇到duty cycle issue?

好嘛。谢谢您宝贵的意思

好吧。是偏了点。我想问一你的翻转电平是电流状态下测出来。 我之前在ADE试过将inv的DC调到VDD/2的翻转的电平,但是这样的W/L的瞬态并不是占空比50%的波形输出。占空比是随着时间在不断的变化的。上升和下降沿的时间长短也是相差较大的。这个问题你是怎么看的呢?

感觉这个比较简单易行。

确实是没有经验,之前没有想好测试方案。现在的问题是那个测试的函数发生器产生不了400M的方波,只能产生400M的正弦波。

clock input是单端的,I/O用的是代工厂提供的标准IO。

duty cycle issue 还不知道严重否,但是肯定会有影响。因为我们是送出去测试的。还没开始测试。

标题

chip 已经tapeout 了?如果还没有,那赶紧改成differential driver 就像lvds 或者pecl 。

如果已经tapeout, 看看板子上能不能补救。

如果input 是digital I/O ,这种I/O duty 不能保证

如果用的是analog I/O + INV ,duty 可以在板上调一调

板上用电阻做个1/2VDD分压,然后通过电容AC couple驱动。那么调整电阻就能调整trigger point 和clk duty 。

你内部的inverter chain 的gain 会把sine 逐级放大到full swing

chip 是已经tape out 了。I/O是代工厂特殊的信号IO。单端进去之后是一个差分的双端输出然后是一连串的inv。现在是只能再板子上调了。那个调整的方法可不可以讲得更详细点啊。谢谢。主要是这是我第一次的测试。还有个问题,

400M的正弦时钟信号我们是接了巴伦做阻抗匹配进去的。这个影响不大吧?

正解

那个我昨晚想了一下,您那个方法是不是跟在函数发生器上直接调节直流电平是一个意思啊?还有那个digital IO和analog IO的duty cycle 有区别又是因为什么呢?谢谢

inverter input/output之间接一个电阻

inverter 会被bias到自己的trigger point

上升沿下降沿不一样是因为你N管和P管的驱动能力不一样,但是这都应该是ps级的误差,你周期才400M,是ns级的千分之几的误差都容忍不了?什么工艺的啊?最好用工艺厂提供的stdcell,人家都设计好了。

随时间变化?如果你只是一个INV,我不信随时间变化,如果你后面有大容性负载倒是有可能,但最终一定稳定下来。

用比较器吧

是ps级的差别。我只是想把时钟的误差做的小一点而已。

仅供参考

用反相器latch来纠正占空比

如果1GHz可以这么做?

inverter input/output之间接一个电阻

=> 這是當 gain stage orlatch ..

1Ghzinvert 應該看 process 能力吧..

pll run 1Ghz 在 0.18um 可以 .

想問如果 方波==> 正弦波該如何變?

level shifter加上 inverter,而且是三级inverter调整pmos 和 nmos的宽长比。个人做过,可以达到duty 正负5%。

谢谢提供的信息