关于pll噪声仿真问题

时间:10-02

整理:3721RD

点击:

小弟最近在做pll的噪声仿真,通过pss+pnoise仿真出各模块的噪声

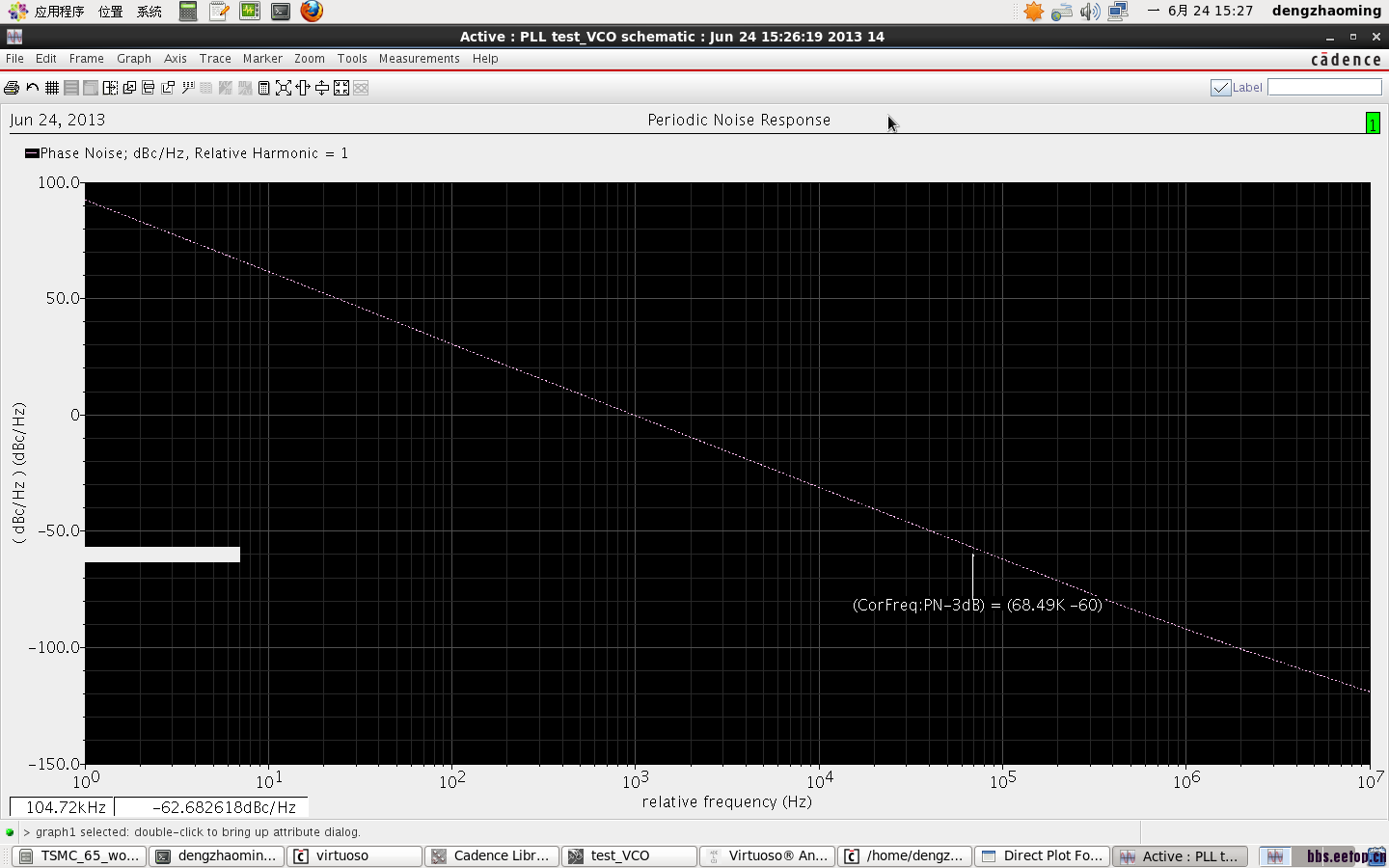

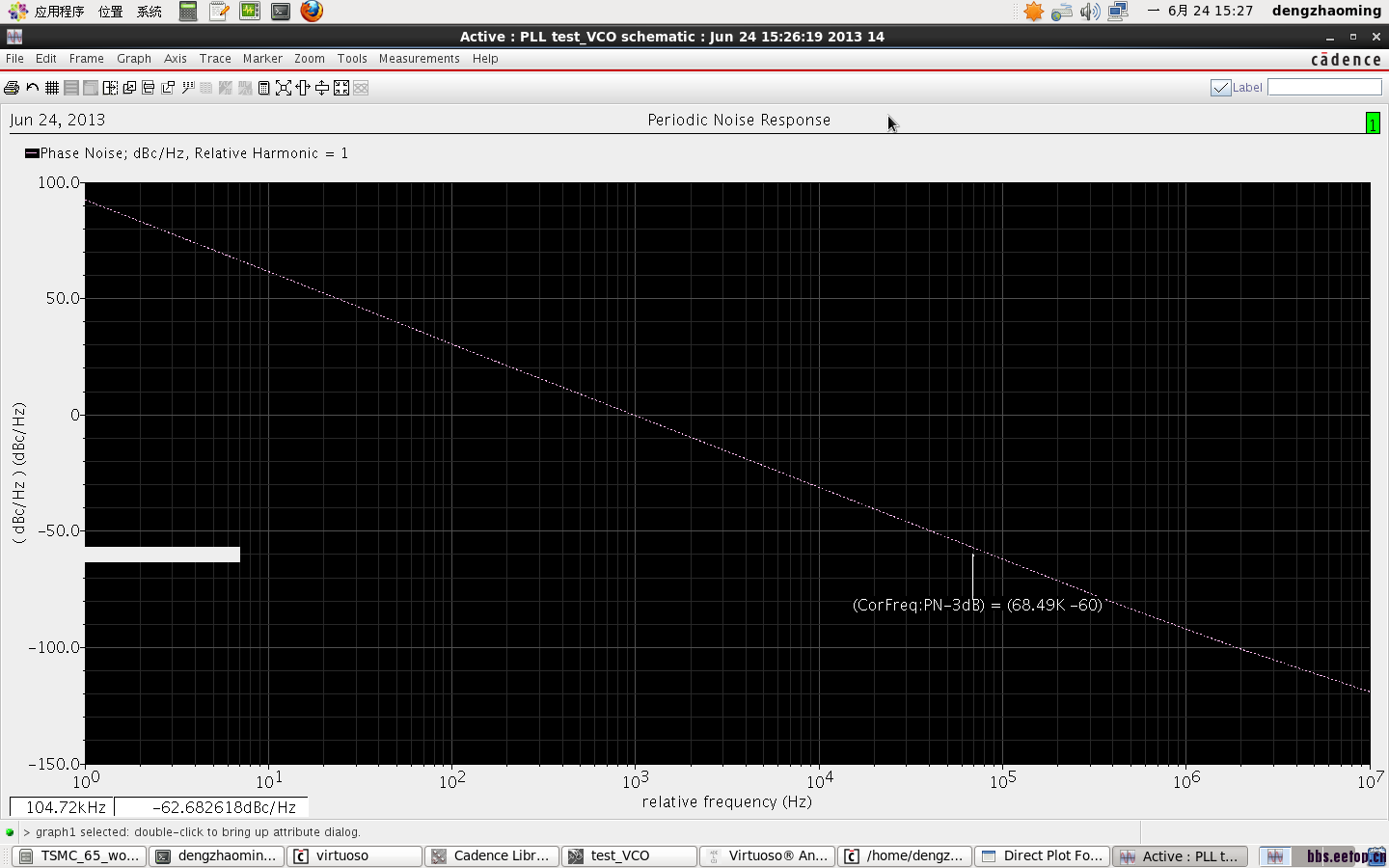

下图是VCO的仿真结果,频率为1.38G

这个图是正确的吗?为什么会有100dbc/Hz这样的结果?

另外,假如所有模块都有pss+pnoise的结果,通过传输函数建模出来的结果就是最后的噪声值嘛?通过tran仿出来锁定时的jitter与这个结果是什么关系呢?

下图是VCO的仿真结果,频率为1.38G

这个图是正确的吗?为什么会有100dbc/Hz这样的结果?

另外,假如所有模块都有pss+pnoise的结果,通过传输函数建模出来的结果就是最后的噪声值嘛?通过tran仿出来锁定时的jitter与这个结果是什么关系呢?

自己顶一个

同问。。

不太清楚你的意思,不过貌似你这VCO性能不咋地啊,是RING VCO吧?

小编的“为什么会有100dbc/Hz这样的结果?”是在惊叹性能太好,对吧? 好像-90dbc/HZ@1M,对ring osc应该还算靠谱吧菜鸟我猜测

我也认为你这性能不咋地。

是ringVCO哈,就是想请教一下为什么会有正的值出现呢?按我自己的理解应该都是小于0的值。

就是一个普通的ringVCO,想请教一下为什么会有正值的出现呢?按我自己的理解应该都是小于0的值。

理论上说在小于1Hz时会有可能出现大于0dBc/Hz的情况的。实际上由于仿真器和模型本身的问题,1/f噪声到极低频的仿真结果是不可靠的,没什么参考价值。有用的是1/f噪声与热噪声的拐角频率以及噪底。

另外个人认为噪声很大程度是种随机现象,是无法用trans仿真的。所以trans仿真出的jitter应该只是周期性jitter,不包括随机jitter。