大家帮忙讲解一下下面这个电路的原理?

时间:10-02

整理:3721RD

点击:

最近学习看到了上面一段资料,理解得不是很明白,大侠们说说自己的理解?

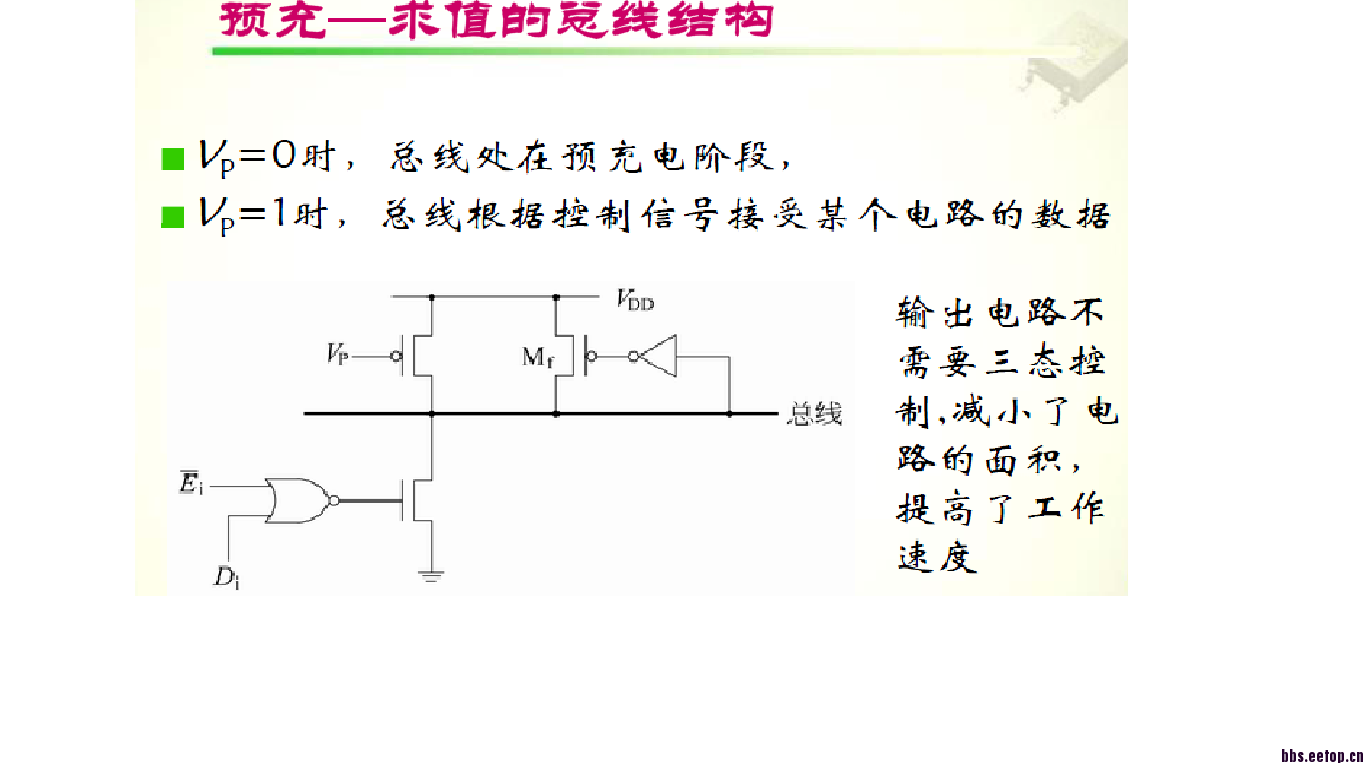

VP等于0的话,总线一直都是高电平对吧,如果VP等于1了,就看下面NMOS的逻辑,如果NMOS栅等于0,总线还是高电平,如果等于1,总线就是低电平

类似多米诺动态电路

VP等于0时,总线为1,当VP由0变成1后,由于Mf和那个INV形成了一个反馈回路,这时虽然VP变成了1,但是Mf还是导通的,如果这时下面那个NMOS的栅极是1,这个NMOS也导通了,Mf和下面那个NMOS同时导通,即电源VDD到地导通,这时总线是1、0、还是高祖z?

右边那个PMOS管是用来加快逻辑电平从0变到1时候的速度用的,通常下边NMOS的管宽长比会大些,放电能力远大于上面的PMOS管,不会出现你说的情况

mf肯定是个相当于电阻的管子,驱动能力很弱,所以这是个于预充求值电路。求值周期内下面Nmos的状态决定了总线的状态。平时总线某个状态(高电平)是固定的,所以说响应速度快。