65nm工艺下锁相环电荷泵漏电问题

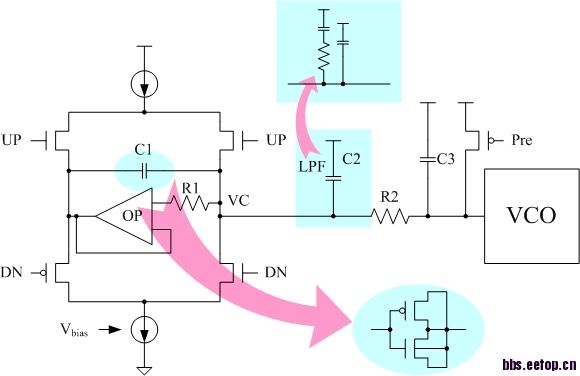

这是一个65nm工艺电源电压为1.8V的PLL电路的CP部分,如图1所示,

图1

ERR:版图的VC无法被PFD拉高(电路图正常)。

原因:估计有两条

1、偏置电压

电路仿真显示:CP上拉、下拉电流源均为130uA;

版图仿真显示:CP上拉、下拉电流源均为60uA;

查到偏置电压:电路仿真为0.4V,版图仿真为0.3V ;

偏置电路如图2所示

图2

但是,我认为这应该不是影响VC上拉的主要原因。

2、漏电流影响

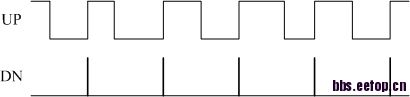

对于UP、DN如图3所示

图3

在UP为0的情况下,VC一直在努力上拉,却不如在UP为1、DN为0的情况下,降低的多。因此,VC的电压一直保持在0.6V左右振荡,但是锁相环的锁定需要VC为1.2V。

由电路图和版图分析,LPF挂的为理想电容,那么出问题的应该是C1和C3,预充电电路及电阻。个人认为最有可能的是C1,是不是65nm工艺导致这个地方的漏电流将VC拉低了。

另有两个问题:

1、

在图1所示的电路中,电阻R1,R2分别起到什么作用?那么图2中R2呢?

2、

C3为MIM电容,容值为0.9pF,我认为R2和C3本身就是一种滤电路,那么这是不是用来滤出纹波的?

3、

如果我想提高Vbias电压,应该怎样调节电路呢?是不是调节R1就可以了?或者帮我分析一下这个电路。

这种LPF结构(电阻,电容接电源,以前都是用的接地),有没有什么好处?和接地的有什么区别?

PIAOGUO

怎么没有人做PLL的了吗?

CP不是很懂,借此问个有点无关的问题,65nm工艺一般不是配合1.2V的电源电压么~

65nm有三种电压:1.2V,2.5V,3.3V,但是为了降低功耗,可以对于1.2V的工艺采用1.0V电压,同理,2.5V可以使用1.8V电压。

多谢~

看了半天,原来还是在后仿阶段,既然是后仿,怀疑什么,都可以debug。比如怀疑漏电就测一下电流好了。我开始还以为是流片回来怀疑这怀疑那。

nice...

C1调小试试看,65nm版图一定要注意寄生效应,千万要对称

那请问,如果是流片回来的漏电,应该怎样解决呢?

不会是栅极漏电或者说是亚阈值漏电?

小编的电路图有问题,左侧的UP和DN控制信号应该和右侧反向才对,两侧开关交互闭合。

LPF是三阶滤波,是不是有部分元件放在片下?这样挂个R1是出于ESD保护吧。

C1的作用不是很明白,以前做过类似的,没用到C1

the up down control signal polarity of differential pair of charge pump ckt in fig 1 is error

and c1 and opamp of figure1 form positive feedback and perhaps it will cause oscillation on vc node

R1 and c1 and opamp of figure1 form positive feedback and perhaps it will cause oscillation on vc node

the sollution is to remove R1 and c1and add compensation capacitor on unity gain buffer opamp output

to prevent oscillation

请问下65nm工艺下 电荷泵设计时的电流范围是?我自己设计的电流500ua,在复位脉冲阶段 上半部分电流冲达到10ma左右 上下电流不匹配 但是当把充放电电流降到100ua一下 基本可以做到电流的匹配想问下 是不是65nm的工艺下电流选取 基本偏小

不需要很大的I,数个G规模的100uA以内足够了!

恩 好谢谢 哪我想问下:

1、你说的这个电流在100ua以内,这个是受什么限制的?

2、你知道关于小编图1中,C1、R1两个参数的取值是怎么定的不?

想问下 你的第一张图中R1 C1的值是怎么选取的 正在设计cp不知道怎么选取这两个参数 指导下吧

charge pump 为高频信号, 不可以使用core devices, 必须用2.5V的..

你确定所用UP控制的两个开关是一样的而DOWN所控制的是不同的?

可以检查下漏电流以及过冲电流PS:你的电荷泵跟CP有没有仿等效相位噪声?我的CP输出电压在仿等效相躁时输出不稳定,总是飘得很求解?