流水线ADC的VREF随时间缓慢变化

时间:10-02

整理:3721RD

点击:

最近做一个12Bit的流水线ADC,参考电压采用带隙基准生成电压+片外uF电容的结构,在仿真中,发现Vref参考电压会随着时间缓慢变化,每个周期变化一点点,100us大概变化了0.0003V,(Vref+缓慢减小,Vref-缓慢增加),。 我的采样开关用的是CMOS结构(PMOS尺寸:100u/0.6u; NMOS尺寸:50u/0.6u),是不是时钟馈通或者电荷注入效应导致Vref缓慢变化?这个开关尺寸是不是太大了?还是要选择合适的额NMOS和PMOS的比例,让沟道电荷注入效应抵消。

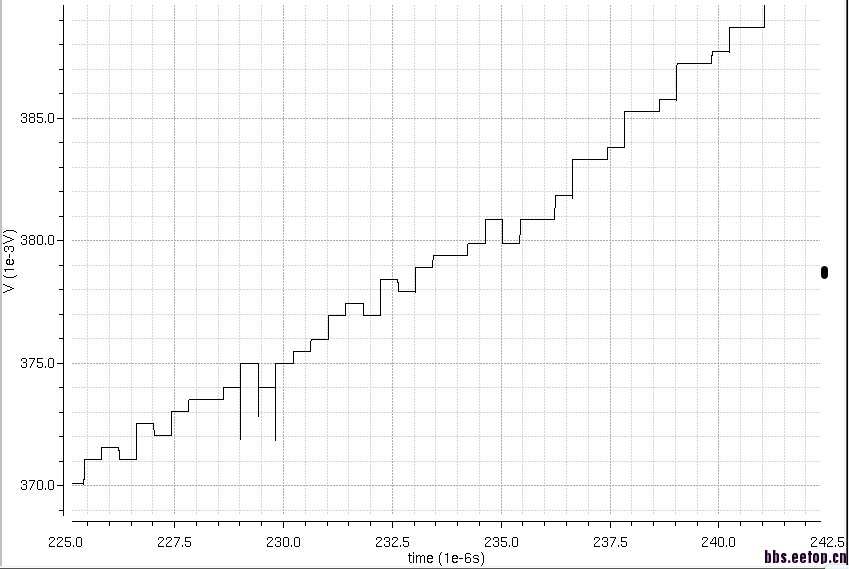

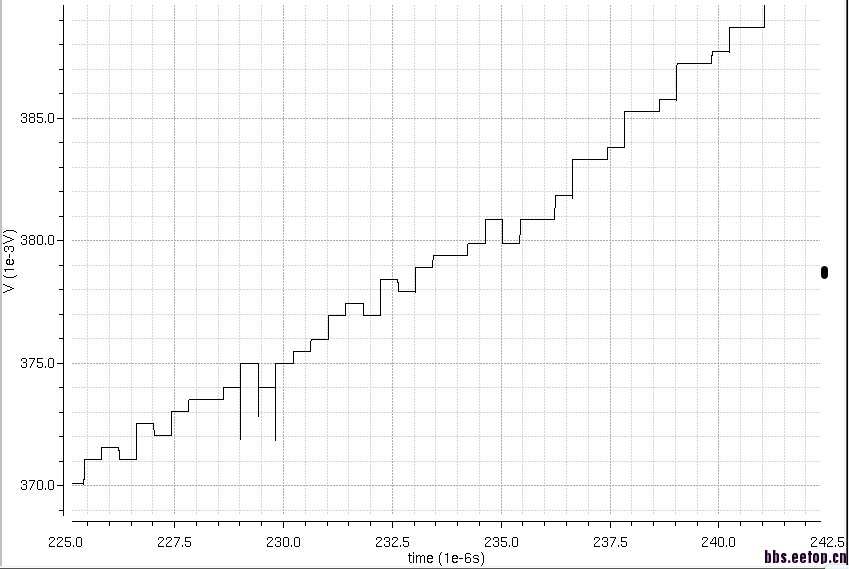

VREF+的仿真结果如下图:

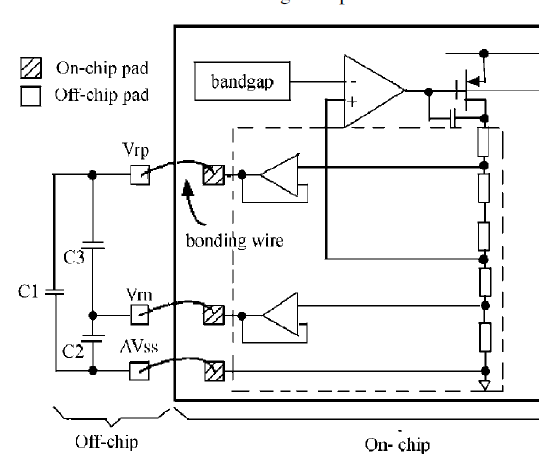

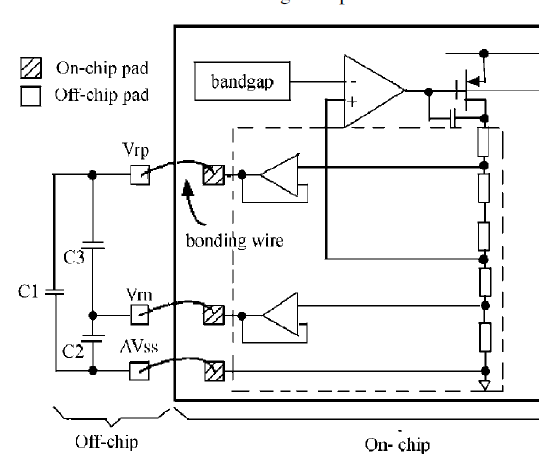

VREF生成电路如下图

仿真发现INL和DNL比较差,是不是和VREF参考电压的缓慢变化有关系?

VREF+的仿真结果如下图:

VREF生成电路如下图

仿真发现INL和DNL比较差,是不是和VREF参考电压的缓慢变化有关系?

vref 动是正常的,

你的ADCfunction有问题,simulation 不应该看到非单调出现

我做的是12Bit的ADC,参考电平的噪声应该小于1/2^13=0.1mV吧,我这样VREF单调减小,会不会导致ADC输出结果随时间变化?

还有,您说的ADC function功能有问题,从波形上看可能是哪个地方出了问题?

看你ref3.6v应该是5v电源吧,Vppdiff至少有1v吧,那应该是1/4096=0.25mv,你怎么算出是0.1mv?用理想ref试试,看着功能是不正常

对的,是5V电源,我想让波动小于 1/2LSB,就是1/2^13,约0.12mV。

有上下参差的原因找到了,一个原因是最后的flash参考电压有大幅波动,修改下电路稳定下来,波形就好很多了,另一个原因是比较器在临界阈值附近有振荡,振荡原因好像是输出端受到CLK的影响反馈到输入端引起的。

VREF像这样的偏移会对ADC的性能有影响吗?是不是要修改开关尺寸消除沟道电荷注入效应和时钟馈通效应对它的影响?

这个比较器可以加点迟滞么?这样就不会振荡,但不知可否加迟滞。

片外cap的话,ref变化实际上不是单调的,可能一会儿向上一会儿向下,如果采样速度不高(你的是2M?)应该问题不大,可以尝试把ref buffer做快,看你ref波形还没稳定到一个小区间内,可能仿更长时间能说明些问题,

是的,仿长时间之后发现在100us之后电压开始稳定下来,波动在0.01mV。