ldo的直流工作点问题

时间:10-02

整理:3721RD

点击:

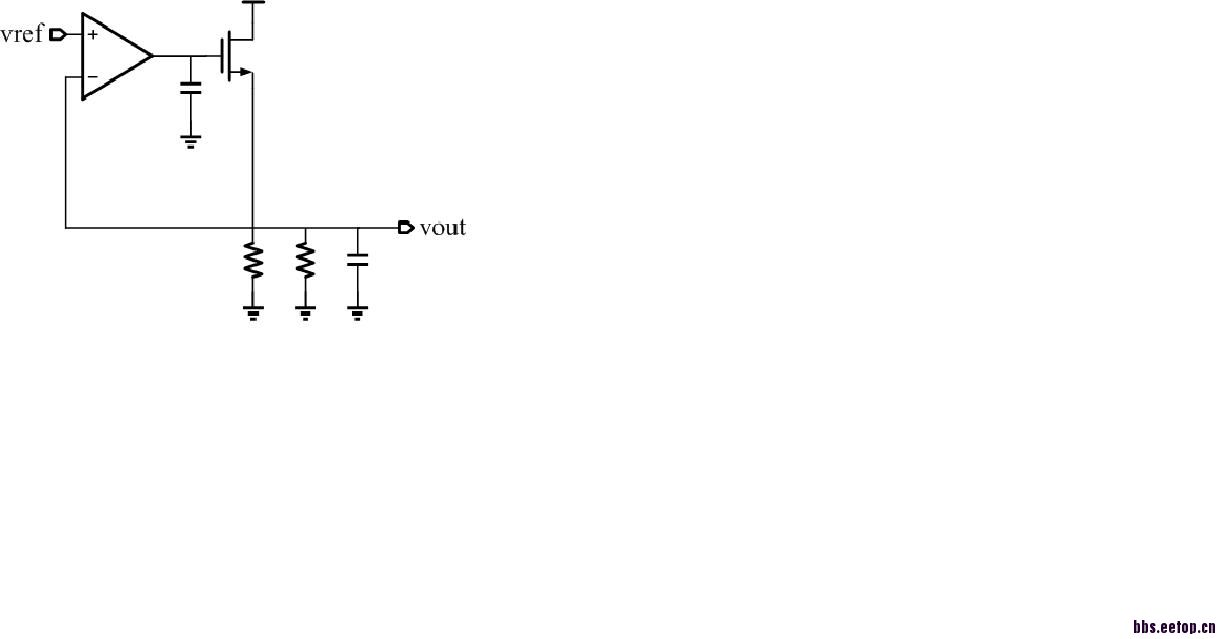

各位大神,上图是我的ldo中的regulation loop,仿真的时候发现参考电压vref和输出电压差的特别大,不知道是什么原因,我的误差放大器的增益有50多dB,按理说也不应该差的太多吧(误差跟vef一样大),请前辈们指教,到底问题出在了哪里?

电源电压多少?VREF多少? 你提供的信息太少了,你仿真工具到期了,看波形软件出错了,地球转太快了,你们家旺财乱按错了键盘了,外星人入侵的可能都不是完全没有。

nb

想象力丰富,估计是SOURCE FOLLOW工作不正常

我的电源电压是2.5V,参考电压1.2V,我刚接触LDO,新手一个,有些问题提的可能不太恰当,我可以理解为你上述说的话是讽刺吗?

有种可能性是你的NMOS尺寸取得太小了以至于NMOS的栅顶到了天(2.5V),都不能提供所需的电流。你先看看NMOS的栅电压是多少,然后用饱和区的Id公式算一下,你的尺寸取得合不合适。

你先确认一下图中NMOS管的gate是否已经到了电源电压了。

如果是这样,还是将其改为PMOS吧。

谢谢大家的回答,现在问题已经解决了,昨天发这个问题的时候确实有些笼统,跟大家解释一下,这个电路是我的ldo的一部分,我在这个电路的输出端加了一个ipulse来仿真load regulation,我设定的ipulse的最低值使得流过负载电阻的电流为负数,于是图中NMOS管的vds<0了,所以整个ldo根本就没有工作。