veriloga形成的vcvs在spetre仿真报错

时间:10-02

整理:3721RD

点击:

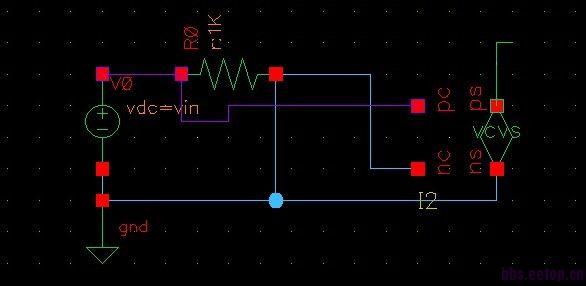

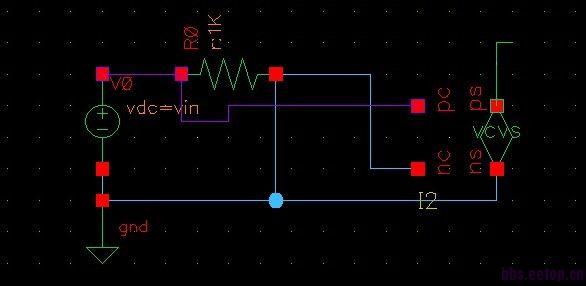

想实现输出电压v=某电阻上的电流*电阻一端对地的电压。电路图如下,右边为veriloga形成的模型

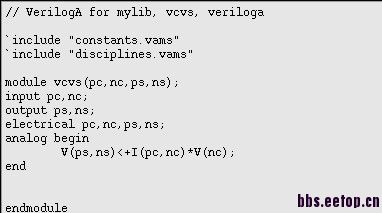

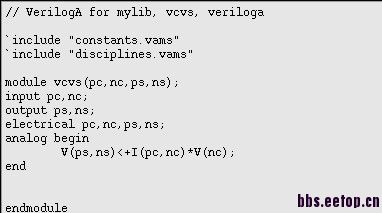

veriloga代码如下

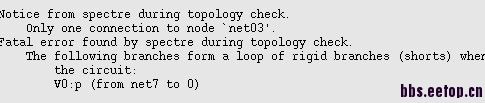

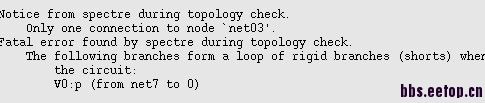

仿真报错如下

net7为紫色的那条线

veriloga代码如下

仿真报错如下

net7为紫色的那条线

你这个错误基本上属于对代码不是理解得很深刻。

nc,pc是个输入端口。如果你不去定义这个端口的I/V特性的话,那么如果你在命令行里面只读取V(ps,ns)的话就是令输入端口的阻抗为无穷大;如果你在命令行里面只读取I(ps,ns)的话就是令输入端口的阻抗为无穷小。但是你同时读取V和I,就让我看不懂了,你贴出来的报错也不全,我也不知道系统把你的ps和ns之间认为是短路还是开路。但是你最大的错误就是无论是短路还是开路,你这电路都接的有问题。如果是短路,你把电压源短掉这是要闹哪样;如果是开路,那就不可能读出电流来。

所以我感觉你的错误不仅在于对verilogA的端口有没有定义I/V特性;最重要的是,你这电路让人不知道你想干啥,概念不太清晰啊。

你开头给的中文公式 和你给的 veriloga的公式表达的意思 都不一样。

谢谢,我修改后的代码可以仿真了,得到了电压*电流的输出。

电路图还是一样,代码改成

inout pc,nc,ps,ns;

....

v(ps,ns)<+v(pc,nc)/1*V(nc);//1为电阻值,把ro改成1ohm

end