阈值电压问题

时间:10-02

整理:3721RD

点击:

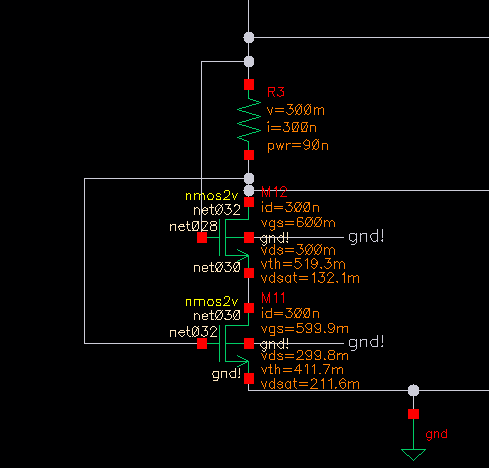

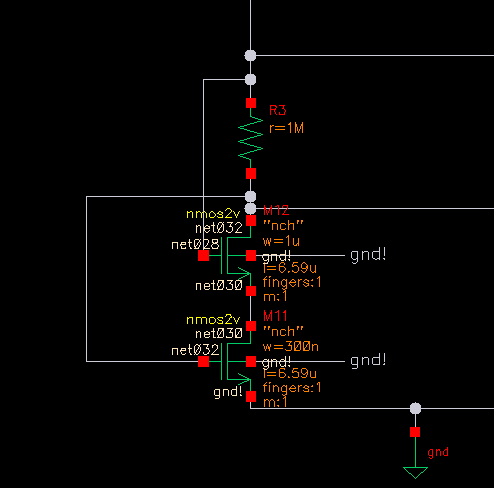

我有个关于阈值电压的问题,当两个nmos管串接时,Vgs 相同的情况下,要Vds一样,上面一个的宽度要大得多。上面一个的阈值电压为啥要大些?

衬偏效应。

显然是上面一个有体效应呗....

基础太差!

楼上不厚道

大家都是从新手过来的,不要鄙视人家啊,如2、3楼所说,上面的管子VSB≠0,下面的管子VSB=0,所以是衬偏效应,上面管子阈值或许会大很多。

上面的NMOS的Vbs<0,引起衬偏了

6楼正解。

顶新手, 多问多交流才能进步

除了body effect, 可能还有一个原因

不知道你cascode nmos 的 channel length是不是一样

如果是.18um以下的工艺,通常L越大,Vth越小

你这个是smic018?在.13的工艺中,我也发现了L越大,阈值越小,这可与微电子器件理论里的结论相反,那里说的由于短沟道效应,Vt随L的减小而减小,不知道为什么

L在多大范围的现象?如果L很小短,可能会看到RSCE,反短沟效应。在90NM或以下比较明显,没注意.13的情况。

可能是大家对工艺和器件不太熟悉,我在好几年前就在坛子里发过帖子解释过这种现象

大家正常思维都是短沟道效应,length越短,Vth越小,这只是针对比较老的工艺和器件结构

从180nm开始,器件结构改变,

所以我准备写个帖子解释这个问题衬偏效应

不错。呵呵

有劳了,相信很多人会因此受益的。

据我所知,反短沟效应和器件结构有直接关系,尤其是和为了减小短沟效应采取的halo注入,不知这种技术从什么尺寸开始使用?是180nm吗?期待发布帖子

不要鄙视新手啊 你们老手都是从新手过来的 5L说的对

言而无信?期待大牛出现

我已经写了一个帖子详细解释反短沟道效应,你可以搜索一下

这个是衬偏效应了,衬底电压反比于阈值电压