Sansen书中的一个轨到轨电路,怎么看都觉得是错的,求指教。

时间:10-02

整理:3721RD

点击:

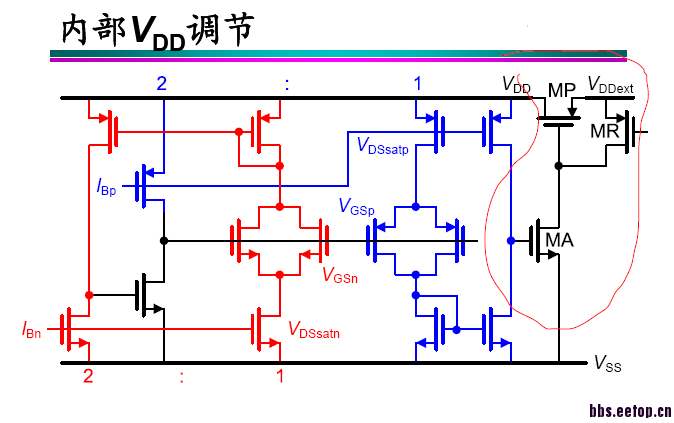

书上P221页的轨到轨电路,VDDext来产生VDD内部电压1.3V,图中我把稳压部分圈出来了,可是这是正反馈电路呀,

VDD处断开,VDD上升,MA的gate处上升,MP的gate下降,VDD又会上升,这不是正反馈吗?怎么成稳压电路了,求论坛大侠指教呀。

这个电路稍微有点意思,反馈环路不只是右边那个圈里哦,你最主要的疏忽是VDD上升,MA的gate不一定是上升的,因为下拉也会变强,当P型差分对的微电流源的VDS>Vdsat的时候,VDD的上升将导致MA的gate下降,所以实际上还是负反馈;整个电路的左侧也是很重要的反馈环路一部分,不能只看右边的,左半侧的保证的是4个差分对管的gate电压等于Vdsatn+Vgsn,右半边蓝色的保证这个电压到VDD为Vgsp+Vdsatp,希望对你有帮助

不明白为何MA的gate会下降,如果VDD上升,PMOS对下面是current mirror呀,MA的gate应该是随电流镜的gate相同变化的,为何会下降呀?能再讲清楚点吗,谢谢还有就是左边的电路将VDD固定在1.3V左右,那么为何电流源的VDS是VDSAT,比VDSAT大一些问题又出在哪里呢?

我怎么觉得VDD上升的调节作用比VDD下降的调节作用弱很多呢?

望大神来看看

书上这个图前面的部分提到了bias是不变的,由VDD_EXT产生的并且Ibp和Ibn相等,那么当VDD上升的时候,电流源P管的gate电压跟着上升保持Ibp恒定,所以MA的gate端的上拉其实是基本不变的;但是下拉会由于VDD的上升而增大,原因就是下拉是电流镜像过来的,VDD上升将使得P型差分对的尾电流源管子的vds增大(左边的电路把4输入管的gate嵌位在Vdsatn+Vgsn),导致这一路的电流增大,那么MA就会因此而下降

大家都寂寞

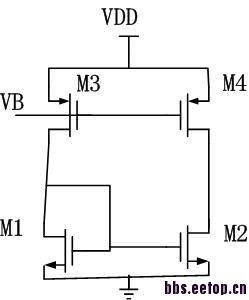

非常感谢您的解答,但是我还是不明白,见附件的图,我把PMOS输入对省略了,VDD上升,VB会上升的,M1的gate也会上升,但是此电路是current mirror,那么M2的drain端和M1的drain必然是相同变化的,M1和M2的gate和drain相同的。那么M2不是一定会上升的呀。我错在哪里呀?