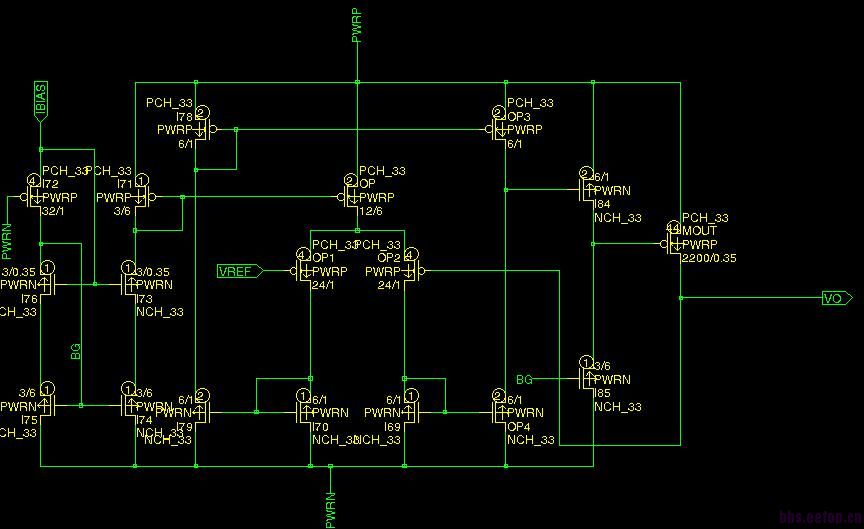

關於LDO stability

在full-load (250mA)gain大約45db phase noise大約40度(雖然很爛)

不過重點在於light load時(2mA)的gain和phase margin整個爛光

vo會被拉到3.3v附近導致input op2 cutoff

op3的 drain也被拉到3.3v

不知道版上神人有什麼看法呢

没有补偿,Iload小了自然不稳定

觉得倒不是稳定性问题呢。2mA load时,Vo拉到3.3V,所以放大器的输出被拉到电源,由于源级跟随器的作用,功率管的栅极到电源有一个VGS的压降,而VDS约为0V,也就是功率管到了线性区。即使功率管工作在这样的线性区内,仍然能流出2mA的电流给load。所以感觉更像是2mA情况下,直流工作点设计的不合理。当然,由于这是一个反馈环路,按理说因为反馈的作用会将直流工作点安排在合理的值上,是否是因为MOS管尺寸选择的问题。

功率管的大小由最大的电流决定了,所以在这种情况下,如果将源级跟随器的VGS减小,是否会有帮助?也就是修改MOS管尺寸让刚才这样一个不正常的稳定态无法存在。

source follower電流減少對輸出到大size PMOS gate端的電壓有限

如果說要做feedback有什麼好的建議呢

结构有点问题,直流工作点(OP)估计很难调好,试试用pmos做源随器?。

I84 这个器件 一般是用PMOS 实现的,实现一级OTA与输出的隔离,是起到buffer的作用

即使采用这个结构,还是要补偿的,二阶OPA

这个结构按说输出电流最大的时候是worst case,轻载的时候更稳定才对。你的电路轻载的工作点不对了,I84不能用NMOS,NMOS的vgs drop (同时有很大的body effect)大过PMOS的VTH,导致power PMOS不能关闭,使VO拉到电源。

空载的时候功率管关不住,即使OP3漏到VDD,功率管的栅源之间都还有一个VGS。

工作点都不正确看小信号仿真没有意义

第二级用PMOS可以解决空载时的这个问题,看看你full load时候会不会有类似的问题吧,如果不满足要求可以修改结构,buffer去掉,更改补偿方式

感謝各位大德的建議 我會再重新調看看