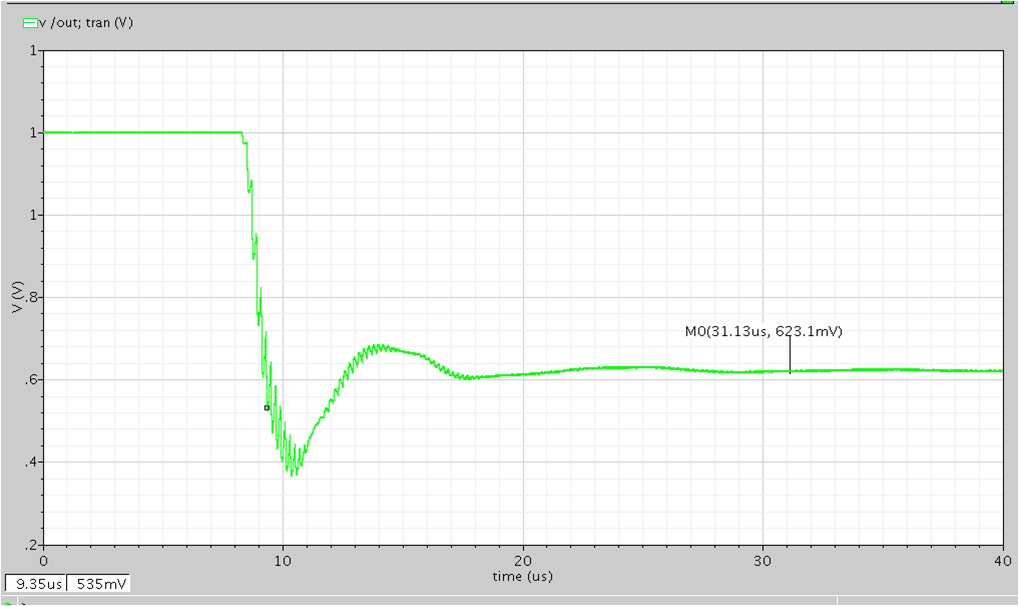

PLL仿真结果的分析

时间:10-02

整理:3721RD

点击:

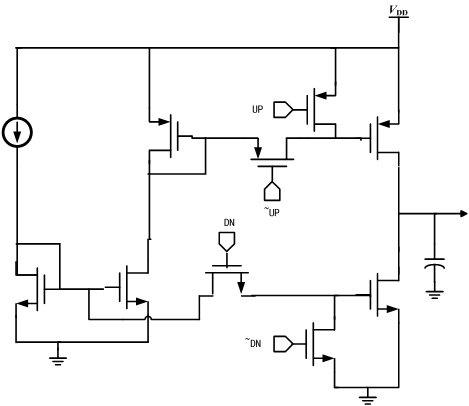

如图所示是我仿真PLL时控制电压的输出结果,我觉得奇怪的是Vtrl的值应该是从0V开始上升,可是我这里却是从电源电压开始下降,可是我并没有在仿真的时候给予Vtrl一个初始值,照理说应该是0V才对呀,还是说由于一开始CP没有工作,CP所有的管子都不工作,使得输出就是为电源电压?CP的电路图如上所示,请各位同学帮我看看!感激不敬!

电路可能有多个简并点,仿真的时候最好初始化一下

为什么是从10us vc才开始下降,即便vc初始值为vdd,那也应该使能之后就开始有下降的趋势啊,感觉是不是哪个信号设置的有点问题,

给vc赋 一下初始值0 看咋样

你的电路有可能是初始CHP截止状态时PLL-UP比PULL-DN强,所以就把VC拉高了

这个电路里应该不存在简并点的问题吧,难道在CP电路里面再添加一个启动电路?

这个仿真结果就是VC=0的时候,应该是我的CP一开始就没工作?

我也觉得应该是CP出问题了,

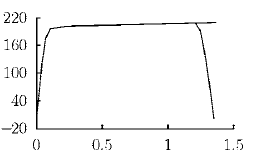

但是我不知道应该怎么调节才能有这样接近的输出,但是我的管子电压稍微变化,电流的变化也很大。应该如何调节呢?