如何从ADC的输出波形中判断出误差来源?

时间:10-02

整理:3721RD

点击:

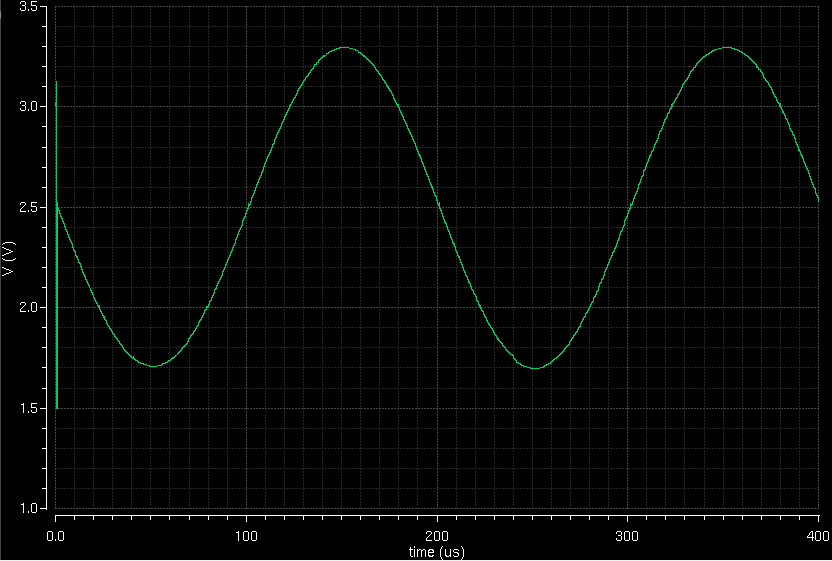

最近做了一个12Bit的ADC,SHA和第一级2.5Bit MDAC用的是带增益自举的折叠共源共栅运放,后面都是1.5Bit MDAC,用的是折叠共源共栅运放。将一个正弦信号转换后的12位数字结果用理想的DAC转换成模拟波形,如下图

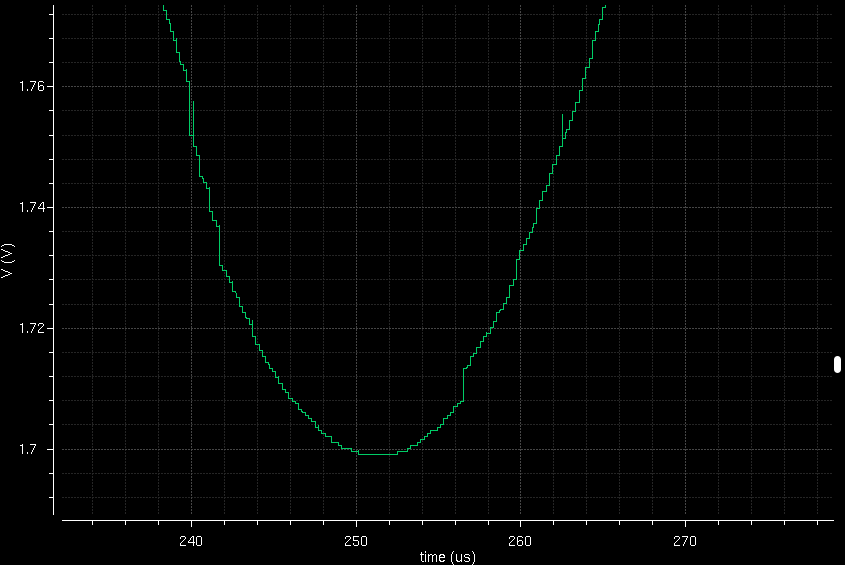

发现这个波形和正常正弦相比,有很大的误差,看某个波段的细节图片如下:

从细节上可以看到输出结果高低层次不齐,但是总体上维持了正弦的形状。

请问这种误差产生的原因是什么?是来源于比较器的Offset误差?还是开关电容电路里的误差?或者是运放的有限增益或非正常建立?

发现这个波形和正常正弦相比,有很大的误差,看某个波段的细节图片如下:

从细节上可以看到输出结果高低层次不齐,但是总体上维持了正弦的形状。

请问这种误差产生的原因是什么?是来源于比较器的Offset误差?还是开关电容电路里的误差?或者是运放的有限增益或非正常建立?

可能是级间增益不够,导致传输曲线上的斜率偏小比较多,造成失码。

您是说MDAC里的运放增益不够,导致实际放大倍数小于2造成了最终结果出现大量失码,是吗?

嗯。可能是。你先仿真下方波输入 在指定的半个周期内能不能建立到需要的精度。

谢谢,我查一查各级运放的建立精度。请问建立精度是选择误差0.1%,还是根据Vref/2^(N-M)来判定?N-M是剩余需要转换的Bit数

有个问题顺便问下,在当前级采样信号阶段,也是上一级的信号保持建立阶段,对吧。在信号采样时,比较器的时钟该如何选取呢?

我设计的时序如下图,在CLK1的高电平(100ns)持续大概80%(第80ns)时采样,95%(第95ns)时停止,这个触发脉冲的高电平持续时间大概5-15ns(半周期约100ns)。这样设计比较器的触发脉冲是否正确?