tsmc0.25工艺做calibre的lvs,原理图netlist不识别电容,管子类型

是不是,原理图的MODEL名字与版图提出来的器件MODEL名字不一样,才对不上,最好把error信息,也贴下啊

您好,这是提示的错误,我看了一下schematic和layout里面的model都是nmos_rfw5,是一样的啊,呵呵

您好,这是提示的错误,我看了一下schematic和layout里面的model都是nmos_rfw5,是一样的啊,呵呵

1) 把lvs.rep报告贴出来

2)把shcematic 产生的CDL网表贴出来

这是报出来的lvs.report

##################################################

####

##C A L I B R ES Y S T E M##

####

##L V SR E P O R T##

####

##################################################

REPORT FILE NAME:delete.lvs.report

LAYOUT NAME:/home/cwjia/lna_tsmc025/delete.sp ('delete')

SOURCE NAME:/home/cwjia/lna_tsmc025/delete.src.net ('delete')

RULE FILE:/home/cwjia/lna_tsmc025/_calibre.lvs_

CREATION TIME:Thu Sep 13 01:50:40 2012

CURRENT DIRECTORY:/home/cwjia/lna_tsmc025

USER NAME:cwjia

CALIBRE VERSION:v2009.1_17.14Mon Feb 16 12:59:40 PST 2009

OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers of instances.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

INCORRECTdeletedelete

**************************************************************************************************************

LVS PARAMETERS

**************************************************************************************************************

o LVS Setup:

// LVS COMPONENT TYPE PROPERTY

// LVS COMPONENT SUBTYPE PROPERTY

// LVS PIN NAME PROPERTY

LVS POWER NAME"AVDDBG" "AVDDR" "AVDWELL" "VDWELL" "VD33APST" "VDD5V" "TAVD33" "VD33PST" "AVDD" "TAVDD"

"TAVD33PST" "TAVDDPST" "AVD33B" "VDD" "AVD33G" "DVDD" "AVDDG" "AVDDB" "VDDG" "VDDPST"

"VD33REF" "VD33" "AVD33R" "VDDSA"

LVS GROUND NAME"VSSPST" "AVS33R" "AVSSUB" "VSSREF" "VSSAPST" "VS33APST" "DVSS" "AVS33G" "AVSSBG" "TAVSS"

"AVS33B" "AVSSB" "GND" "VSSG" "VSSUB" "VSS" "AVSS" "TAVSSPST" "AGND" "AVSSR" "AVSSG"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESALL

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESNO

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLENO

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVS INJECT LOGICYES

LVS EXPAND UNBALANCED CELLSYES

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSYES

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

// LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

// LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE SCALE X PARAMETERSNO

LVS SPICE STRICT WLNO

// LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LVS EXACT SUBTYPESNO

LAYOUT CASENO

SOURCE CASENO

LVS COMPARE CASENO

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM50

LVS PROPERTY RESOLUTION MAXIMUM65536

// LVS SIGNATURE MAXIMUM

LVS FILTER UNUSED OPTIONAB RC RE RG

// LVS REPORT OPTION

LVS REPORT UNITSYES

// LVS NON USER NAME PORT

// LVS NON USER NAME NET

// LVS NON USER NAME INSTANCE

// Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARYES

LVS REDUCE SERIES CAPACITORSYES

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESYES

LVS REDUCErppoly_rfPARALLEL [ TOLERANCE L 0 ]

LVS REDUCErppoly_rfSERIES PLUS MINUS [ TOLERANCE W 0 ]

LVS REDUCErppolywo_rfPARALLEL [ TOLERANCE L 0 ]

LVS REDUCErppolywo_rfSERIES PLUS MINUS [ TOLERANCE W 0 ]

LVS REDUCTION PRIORITYPARALLEL

// Trace Property

TRACE PROPERTYmn(nm)l l 2

TRACE PROPERTYmn(nm)w w 2

TRACE PROPERTYmn(n1)l l 2

TRACE PROPERTYmn(n1)w w 2

TRACE PROPERTYmn(nl)l l 2

TRACE PROPERTYmn(nl)w w 2

TRACE PROPERTYmn(n)l l 2

TRACE PROPERTYmn(n)w w 2

TRACE PROPERTYmn(n2)l l 2

TRACE PROPERTYmn(n2)w w 2

TRACE PROPERTYm(y)l l 2

TRACE PROPERTYm(y)w w 2

TRACE PROPERTYm(c1)l l 2

TRACE PROPERTYm(c1)w w 2

TRACE PROPERTYmn(nd)l l 2

TRACE PROPERTYmn(nd)w w 2

TRACE PROPERTYmn(nz)l l 2

TRACE PROPERTYmn(nz)w w 2

TRACE PROPERTYmn(nn)l l 2

TRACE PROPERTYmn(nn)w w 2

TRACE PROPERTYm(c2)l l 2

TRACE PROPERTYm(c2)w w 2

TRACE PROPERTYmp(pz)l l 2

TRACE PROPERTYmp(pz)w w 2

TRACE PROPERTYmp(pd)l l 2

TRACE PROPERTYmp(pd)w w 2

TRACE PROPERTYmp(p)l l 2

TRACE PROPERTYmp(p)w w 2

TRACE PROPERTYmp(ps)l l 2

TRACE PROPERTYmp(ps)w w 2

TRACE PROPERTYmp(pm)l l 2

TRACE PROPERTYmp(pm)w w 2

TRACE PROPERTYq(nv)a a 0

TRACE PROPERTYq(pv)a a 0

TRACE PROPERTYd(dp)a a 0

TRACE PROPERTYd(dw)a a 0

TRACE PROPERTYd(dn)a a 0

TRACE PROPERTYr(lr)r r 2

TRACE PROPERTYr(m5)r r 0

TRACE PROPERTYr(ns)r r 0

TRACE PROPERTYr(m4)r r 0

TRACE PROPERTYr(wo)r r 0

TRACE PROPERTYr(pi)r r 0

TRACE PROPERTYr(nd)r r 0

TRACE PROPERTYr(m1)r r 0

TRACE PROPERTYr(pd)r r 0

TRACE PROPERTYr(nr)r r 0

TRACE PROPERTYr(pr)r r 0

TRACE PROPERTYr(m3)r r 0

TRACE PROPERTYr(ps)r r 0

TRACE PROPERTYr(ni)r r 0

TRACE PROPERTYr(m2)r r 0

TRACE PROPERTYr(wr)r r 0

TRACE PROPERTYrppolywo_rfl l 0

TRACE PROPERTYrppolywo_rfw w 0

TRACE PROPERTYpmos_rf33w5lr lr 0

TRACE PROPERTYpmos_rf33w5wr wr 0

TRACE PROPERTYpmos_rf33w5nr nr 0

TRACE PROPERTYnmos_rf33w5lr lr 0

TRACE PROPERTYnmos_rf33w5wr wr 0

TRACE PROPERTYnmos_rf33w5nr nr 0

TRACE PROPERTYpmos_rfw10lr lr 0

TRACE PROPERTYpmos_rfw10wr wr 0

TRACE PROPERTYpmos_rfw10nr nr 0

TRACE PROPERTYxjvarn n 0

TRACE PROPERTYxjvarpj pj 0

TRACE PROPERTYxjvara a 0

TRACE PROPERTYrppoly_rfl l 0

TRACE PROPERTYrppoly_rfw w 0

TRACE PROPERTYmimcaplt lt 0

TRACE PROPERTYmimcapm m 0

TRACE PROPERTYmimcapa a 0

TRACE PROPERTYmimcappj pj 0

TRACE PROPERTYspiral_turnnr nr 0

TRACE PROPERTYspiral_turnrad rad 0

TRACE PROPERTYspiral_turnw w 0

TRACE PROPERTYspiral_turns s 0

TRACE PROPERTYnmos_rf33w10lr lr 0

TRACE PROPERTYnmos_rf33w10wr wr 0

TRACE PROPERTYnmos_rf33w10nr nr 0

TRACE PROPERTYnmos_rfw10lr lr 0

TRACE PROPERTYnmos_rfw10wr wr 0

TRACE PROPERTYnmos_rfw10nr nr 0

TRACE PROPERTYpmos_rfw5lr lr 0

TRACE PROPERTYpmos_rfw5wr wr 0

TRACE PROPERTYpmos_rfw5nr nr 0

TRACE PROPERTYmoscapa a 0

TRACE PROPERTYmoscappj pj 0

TRACE PROPERTYmoscapn n 0

TRACE PROPERTYnmos_rftrw10lr lr 0

TRACE PROPERTYnmos_rftrw10wr wr 0

TRACE PROPERTYnmos_rftrw10nr nr 0

TRACE PROPERTYnmos_rfw5lr lr 0

TRACE PROPERTYnmos_rfw5wr wr 0

TRACE PROPERTYnmos_rfw5nr nr 0

TRACE PROPERTYpmos_rf33w10lr lr 0

TRACE PROPERTYpmos_rf33w10wr wr 0

TRACE PROPERTYpmos_rf33w10nr nr 0

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers of instances (see below).

LAYOUT CELL NAME:delete

SOURCE CELL NAME:delete

--------------------------------------------------------------------------------------------------------------

NUMBERS OF OBJECTS

------------------

LayoutSourceComponent Type

--------------------------

Ports:33

Nets:33

Instances:01*MN (4 pins)

10*nmos_rfw5 (4 pins)

------------

Total Inst:11

* = Number of objects in layout different from number in source.

**************************************************************************************************************

INCORRECT OBJECTS

**************************************************************************************************************

LEGEND:

-------

ne= Naming Error (same layout name found in source

circuit, but object was matched otherwise).

**************************************************************************************************************

INCORRECT INSTANCES

DISC#LAYOUT NAMESOURCE NAME

**************************************************************************************************************

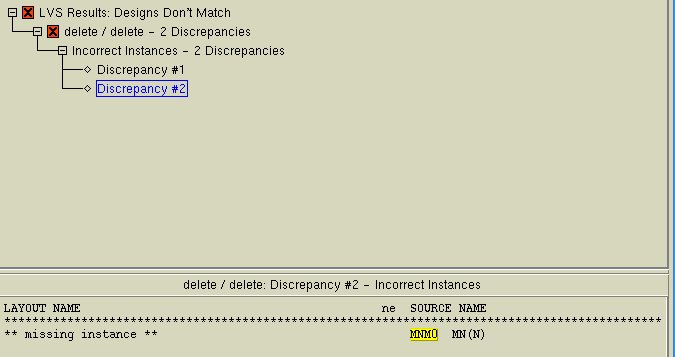

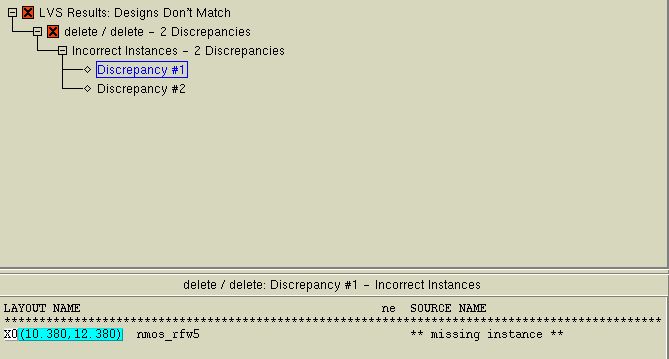

1X0(10.380,12.380)nmos_rfw5** missing instance **

--------------------------------------------------------------------------------------------------------------

2** missing instance **MNM0MN(N)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:3300

Nets:3300

Instances:0001MN(N)

0010nmos_rfw5

--------------------------------

Total Inst:0011

o Initial Correspondence Points:

Ports:G D S

**************************************************************************************************************

SUMMARY

**************************************************************************************************************

Total CPU Time:0 sec

Total Elapsed Time:0 sec

原理图还是没识别管子类型,好奇怪啊

自己顶一下,呵呵

你认为管子的类型到底哪个是对的? MN还是nmos_rfw5?

应该nmos_rfw5是对的,我调用管子的时候都是这个类型滴啊,可能是哪里出了问题呢?

那就是说产生CDL的过程出错了. CDL的结果是直接由CDF参数决定的. 你先看看原理图中调用的那个晶体管的CDF参数是怎么设置的,比如netlist procedure之类的。如果代工厂的PDK所带的SKILL初始化文件没有load进来,也会在CDL上面出错。你看看加载你们工艺库子目录下的libInit.il文件有没有效果。

9#正解,是CDL不一致导致;

你看电路symbol显示时的model和LVS做的model是不一样的;其差异可参考cadence下<<CDF.....>>手册的说明;

如果是安装的PDK,就要像9#那样,load一个skill文件;

如果是自己做的基本库,可考虑在Cadence-->tool---->CDF里面手动修改cdf参数

恩啊,非常感谢,呵呵,我先试试