请教 PSRR仿真的问题

时间:10-02

整理:3721RD

点击:

大家好

在仿真运放时,给电源加了ac信号1v

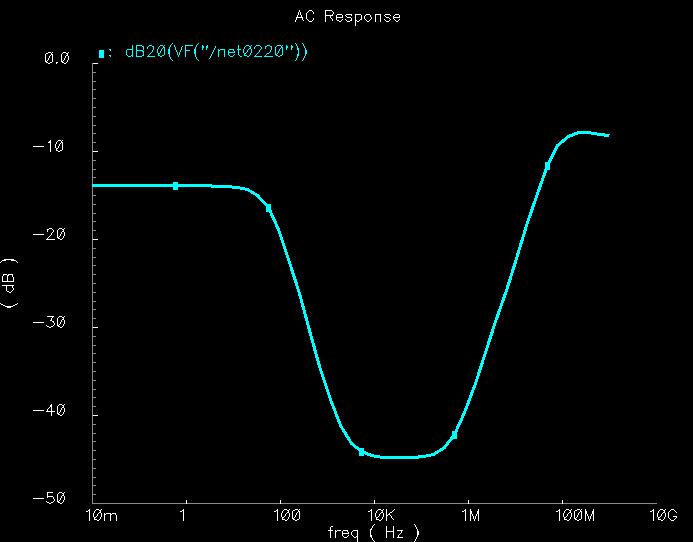

静态工作点正常 ac频率扫描后 测得运放输出端的 增益如图所示

这个增益是由电源引起的吧?

那是不是越低越好吗?

在仿真运放时,给电源加了ac信号1v

静态工作点正常 ac频率扫描后 测得运放输出端的 增益如图所示

这个增益是由电源引起的吧?

那是不是越低越好吗?

100HZ以下怎么这么差?接错了吧?

我在Results-Direct Plot- AC 20DB 然后查看运放的输出端(不是点运放的反馈端吧?)

现在究竟是模拟的天下还是数字的天下。

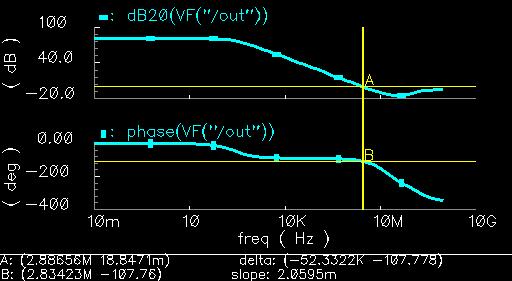

运放增益为80DB 相位107°

大家看下

大家看下

大家看下

运放挺好的啊,你想问什么呢?

请问PSRR够吗?

因为PSRR是随频率变化的

一般怎么样看PSRR是不是达到要求?

谢谢

大家看下 谢谢

大家看下

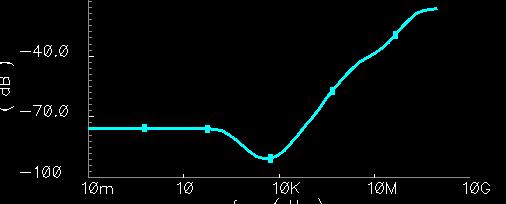

PSRR 主要是针对电源的低频噪音, 因为电源总是有稳压电容相配, 噪音主要是低频. PSRR是个高通特性, 至于说拐点在哪里, 各个公司要求不一, 经验是10K到100K, 抑制比达到-40dB以上就可以了. 因为, 一般芯片上会有个最差的PSRR模块, 例如Bandgap, 主要应该提升它的PSRR.

视乎够了

看具体应用吧

就普遍指标而言还可以

路过,赚个积分

你的PSRR仿真性能很好啊!基本上在低频领域关注100KHz以下的PSRR,看样子你的运放设计的不错啊

16# gongxuwhu 视具体要求而定. 如果是 LDO, 1K时候的PSRR要有75dB。

你电源的AC信号给的频率是多少呢?

如果这是一个LDO, 图应该是在重载下仿的

如此高的PSRR性能,能做到这么平坦的裕度曲线,而且带宽还这么高

本人倒是对你的单极点环路架构十分感兴趣

学习学习!

你的电源上什么频率的噪声最大就关心那个频率的PSRR

学习拉

来学习PSRR的