二级运放输出端电压的问题

时间:10-02

整理:3721RD

点击:

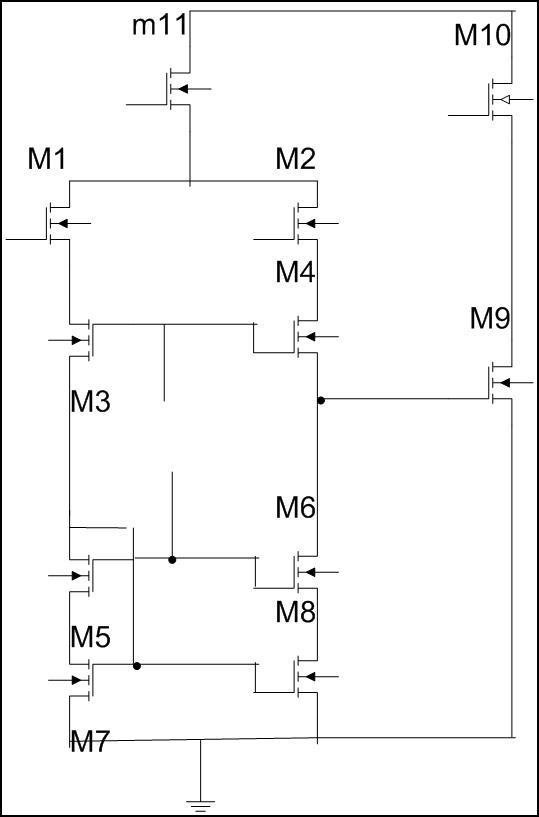

结构图

结构图输入为VDD/2,前仿时输出电压:1.8V, 比VDD/2大不少,是否合理?

后仿时,输出端端电压:316mV,但是其他节点电压都和前仿差不多,这样的话,版图需要改进哪里?

谢谢

你是开环仿真的嘛?如果增益非常大,开环仿出来的电压变化很大

你是开环仿真的嘛?如果增益非常大,开环仿出来的电压变化很大

闭环仿真吧,这个问题我也遇到过,开环仿真的,后仿时可能失调增大导致偏离原有直流工作点,管子无法工作在饱和区,你把环路闭合(用大的电容和电感使之直流环路闭合,交流开路就可以仿真了),然后再在这种环境下仿真幅频相频特性就行了

o谢谢, 那这样的话,流片出来会不会有问题

现在的情况是只要后仿真没问题,流片结果都是功能可以实现,至于性能就不好说了。

全是NMOS?

也可能失配了。

加了共模反馈了么?