基本电流镜仿真结果结果不对,需要注意什么地方

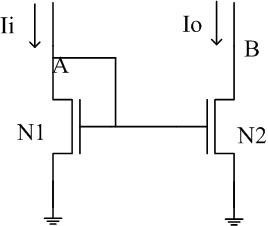

上面是一个基本电流镜,NMOS管N2实现对N1电流的拷贝,设置N1和N2为完全相同的两个NMOS管,我用Hspice仿真来看Ii和Io的情况,理论上应该是完全一致的,可是仿真结果相差很大,如下所图示。

其中横轴时间,纵轴是电压,红线是A点的电流(Ii),绿线是B点的电流(Io),这两个重合的地方很少,我想是我仿真的代码有问题,贴出来请各位指正一下:

.param SUPPLY1=0.9v

vB B0SUPPLY1

.include "D:\avanti\HSPICE\Model\PTM\32nm_bulk.pm"

********************************************************************************

*网表部分

********************************************************************************

MN1 A A GND GND NMOS L=1 W=2*MOS管N1,漏极和栅极接A,源极和体(body)接GND

MN2 B A GND GND NMOS L=1 W=2*MOS管N2,漏极接B,栅极接A,源极和体(body)接GND

********************************************************************************

*激励部分

********************************************************************************

VA A 0 PWL 0ps 0V, 100ps 0V, 10000psSUPPLY*A处产生一个从0V到高电平的电平变化,图中黄线所示

这个地方是不是不对,A点可以 用VA来提供电压吗?B点的Io是不是需要负载?怎样才能仿真这个基本电流镜?感谢您的回答。

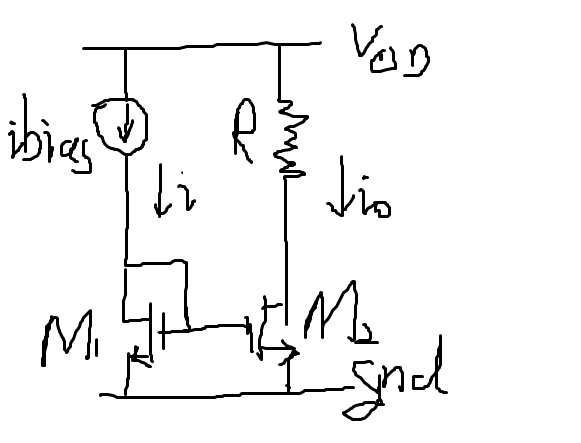

这个是电流镜不是电压镜~按这个图上的仿一下看看~

正解~

感谢您。由于是非电子方面的,我不是太明白。您这里左边红框的ibias是什么?右边红框中的电阻一般在32nm工艺下我取多少仿真比较合适?

1. 用瞬态仿,本身就不对,把电容的影响也夹杂进来了。

2. 32nm工艺下,希望能精确copy,按照你原始的网表看,除非左边的管子drain/gate电压精确0.9v。

谢谢。

1.如果不用瞬态仿真,怎么能体现对不同电流的拷贝作用呢?

2.左边的管子为什么必须到0.9v呢,应该是随着栅源端的电压不同,右边的NMOS拷贝到的电流不同才是啊。

你在A点加电压,不就是等于在右边管子的G上加电压吗?若是带上电阻负载,不就是一个放大器了么?怎么仿电流镜像。

用DC扫描仿,

.param ir=5u

ir vdd 0 dc=ir sweep ir 0 10u 1u

瞬态里有电容特性,你用10ns上升时间看和用10us上升时间看,两边的电流波形重合方式肯定不同。除非你就是在意动态的copy特性,否则这么仿真出来的说明不了什么。你给右边的mos drain已经预设了0.9v电压,那两边电流要精确一致,难道不是要左边的drain 电压也是0.9v?

不知道你这么做仿真的目的是什么,我觉得你在bbs上问,效率太低,应先就近在实验室找个人问问,三言两语就解决了。

是这样的,我们实验室都是计算机专业的,没有人会这个,问过了。我想仿真这个的目的是看看这个基本电流镜是否真的能起到电流拷贝的作用,我想如果能拷贝的话,在Hspice仿真的情况下输入电流的曲线和输出电流的曲线是一致的,我就是想仿真后看看这两个曲线。

好吧,理解。电流镜能复制电流,但是存在误差,两边管子的drain端电压不相等,会造成主要的复制误差,所以我说只有当你左边的gate/drain电压是0.9v时才能精确复制。其余情况,两边电流只是近似相等。当gate电压太高时,甚至连近似相等都谈不上。这些都可以在模电的教科书上找到具体解释。

不能用时间来仿啊,横轴是电压,纵轴是电流啊

呵呵,我门外汉好可怕吧,抱歉的说啊。那我有没有办法实现我的想法,通过Hspice仿真得到电流拷贝的曲线呢?另外,请推荐一本相关的经典书籍如何,谢谢啊

图中电源是否画错,个人认为应该是电流源才是。

按照2楼给的图,我画了一下,如下图:

然后我写了个网表文件进行仿真,文件如下:

.param SUPPLY=0.9v

.option scale=32n

vdd VDD0SUPPLY

.include "D:\avanti\HSPICE\Model\PTM\32nm_bulk.pm"

*************************************************************************

*网表部分

*************************************************************************

MN1 A A GND GND NMOS L=1 W=2 *MOS管N1,漏极和栅极接A,源极和体(body)接GND

MN2 B A GND GND NMOS L=1 W=2 *MOS管N2,漏极接B,栅极接A,源极和体(body)接GND

R1 VDD B 50k *电阻R1,一边接VDD,一边接节点B,电阻是50k欧

Ii VDD A 10U *接在节点VDD和A之间的电流源

*************************************************************************

*激励部分

*************************************************************************

.DC Ii 1U 10U 1U*dc仿真,电流Ii从1uA到10uA以步长1uA变化

.PRINT DC I(Ii) I(R1)

*************************************************************************

* over all

*************************************************************************

仿真结果如下图:

其中黄线是Ii,红线是经过电阻R1的电流I(R1)也就是Io,但是仍然相差很大,请帮忙分析一下。是否晶体管的宽长比不对,或者电阻值设置不对?谢谢。

两个管子尺寸一致,VG VS都相等,理论上电流应该相等

但是由于A点和B点的VD值不等,所以由于二阶效应,电流镜像不准

如果我不是色盲的话,那么黄色的是输入,红色的是输出

VDD太低了取3V试试

没错,线的颜色写反了。两条线偏差比较大。如果仅仅是宽长比相同就可以实现电流复制的话,这里为什么偏差这么大呢?怎么样设置A、B两点的VD值一样呢?

我用的是32nm工艺节点,其标称电压一般是0.9v,我换了3v实验,两条线的偏差也还很大,如下图

你把电路想得太神奇了,好像电流镜只要把两个管子宽长比一致或者按比例,随便给个电流源就能随意复制。

不要仿瞬态,看不出你想要的东西。

首先确定好静态工作点。你把输入电流分别给1u,2u…………10u,先看你的管子的工作状态,工作状态都不对的话,不可能复制。

谢谢。我一开始确实是认为只要满足宽长比一致就能复制电流的,因为没有模电基础,而网上介绍电流镜的都是给出了那个电流复制的公式。但后来发现不是这么简单。我在14楼给出了图和网表文件,还希望指点一下这个错在什么地方。

While trying to copy current it is necessary to set v(A)=v(B). Otherwise you will have VDS modulation and so error. For this process Vth maybe at 0.4V level so your first simulation with 0.9V is more appropriate (3V is too high and so you will have much bigger error due to VDS modulation and other second order effects). If I were you I would not sweep the current but set a value like 0.8uA and VDD=0.9V and sweep R value to find out where to branch currents are equal. When currents are equal I expect V(A)=V(B) would be equal. Once you get equal branch currents than you can sweep input current around that nominal current and observe V(A), v(B) and current mismatch. Current mirrors does not copy every current value so there is a range for current values they work with an acceptable error. Good luck. 而试图复制当前有必要设定V(一)= V(B)。否则,你将有VDS的调制等错误。也许在这个过程VTH为0.4V水平与0.9V的模拟是比较合适的(3V太高,所以你将有更大的错误,由于VDS的调制及其他二阶效应)。如果我是你我不会扫的电流,但像0.8uA和VDD=0.9V和扫描R值设置的值,找出分支电流是相等的。当电流是相等的,我希望V(A)= V(B)将是平等的。一旦你得到平等的分支电流比你可以打扫,额定电流输入电流和观察五(一),V(B)和电流不匹配。电流镜不复制每一个电流值,所以是他们与一个可以接受的错误工作电流值的范围。祝你好运。

1. mos current mirror 得在工作區 ..

constant current 會和 load 有關的

2. mos Vds 會影響到 mirror . 一般要 mirror 夠好就是 L => large

但因此 L large =>W & M 都拉大..

一般 0.5um多選 L >3u5u..要Vds能 1~3v都還能穩定流 ,L=15u W=20u M=6 ..

32nm process analog design VCC 會多低阿?

以下是我对英文部分的理解:

需要设置v(A)=v(B)来拷贝电流。否则会有VDS调制错误等问题。在这个工艺下,Vth可能是在0.4v左右,因此你原来用0.9v的仿真是恰当的(3V太高了,由于VDS调制和其他二阶效应你可能会有更大的错误)。如果我是你,我不会来变动(sweep)电流而是设置大约0.8uA和VDD=0.9V,然后去变动电阻R,这样去找分支电流相等的地方。当电流相等以后,我想v(A)=V(B)大致就实现了。一旦你获得了相等的分支电流,你可以在这个正常的电流值附近变动电流值去观察V(A),V(B)以及电流不匹配的情况。电流镜只能在可以接受的失配范围内拷贝一定范围内的电流而不能拷贝任意电流。祝你好运。

非常感谢您的回复,我试了该方法很好。只是您为什么要确定电流为0.8uA呢?

感谢回复。

2. mos Vds 會影響到 mirror . 一般要 mirror 夠好就是 L => large

但因此 L large =>W & M 都拉大..

一般 0.5um多選 L >3u5u..要Vds能 1~3v都還能穩定流 ,L=15u W=20u M=6 ..

这里,“L large =>W & M 都拉大..”是什么意思啊?L和W是宽长比中的L和W吗?M是什么呢?

32nm process analog design VCC 會多低阿?

32nm制程的标称VCC为0.9V。

Since I do not know your M1, M2, R sizes and models I wanted to speed you up to a good enough point in your simulations. There is no magic about 8.3uA current, I got it from your simulation result curves shown at your post number 14. On your plot with your existing M1, M2 and R values, 8.3uAis giving you aproximately v(A)=v(B) (Eye-balling from your plot I got 8.3uA, so it is aproximate). Now if you like the results while still watching v(A)=v(B) you can change current value provided that you keep current density through M1 and M2 the same i.e. change current and device sizes together so you have same current density on CMOS transistors. If you satisfied with your new nominal current value, device sizes and results than check VDsat=Vgs-Vt of transistors and make sure VDsat is about 200mV for better matching results (If you go closer to weak inversion i.e. 70-100mv of VDsat your mirror error will be worse since Vgs mismatch dominates). I realize Google translation is not as clear as it should be,I do not have any other way, but you understood so it worked. Good luck.

既然我不知道你的M1,M2,研究尺寸和型号,我想加快你在你的模拟足够的好点。有没有约8.3uA电流的魔力,我从你的仿真结果曲线显示在您的后14号。在您与您现有的M1,M2和R值的情节,8.3uA给你aproximately至五 V(A)= V(B)(从你的阴谋眼球我8.3uA,因此它是aproximate)。现在,如果你喜欢的结果,而仍然看至五 V(A)= V(B)你可以改变电流值提供您保留通过M1和M2相同的,即电流变化和器件尺寸在一起让你有相同的电流密度的CMOS电流密度晶体管。如果您满意您的新的额定电流值,器件尺寸和比支票VDSAT= VGS-VT晶体管的结果,使确保VDSAT是为更好的匹配结果约200mV的(如果你去接近弱反转,即70-100mv的VDSAT你的镜子错误会更糟,因为VGS不匹配占主导地位)。我知道谷歌翻译是因为它应该是不清晰的,我没有任何其他方式,但你了解它的工作。祝你好运。

谢谢回复。

1.您说您根据14楼的仿真图得到8.3uA,不过21楼您说的是0.8uA,不过我大致理解了,这个电流值不是最重要的,重要的是要根据电流值保证N1和N2都工作在饱和区,不知道我的理解是否正确?

2.还有一个问题我很茫然,因为电流镜工作在饱和区意味着要满足“Vds≥Vgs-Vth”,由于N1的栅极和漏极接在一起,所以我想N1一定工作在饱和区的,那么是不是只要保证N2工作在饱和区就能保证电流镜的电流拷贝作用?

3.这个地方考虑电流密度的目的是什么?N2对N1能够按比例拷贝电流不就行了么?

Answer to A: It is a typo.Yes you understand it right, For a desired nominal current (and for the desired current range around it) we want current mirror transistors are operating in saturation region. N1 and N2 have a relatively large ~200mV VDsat and V(A)=V(B). Since transistors Gate and sources are common making drain voltages equal sets the both transistors operating conditions being exactly equal so current will copy exactly (within the practical limits due to mismatches etc). Now making V(A) = V(B) is hard in practice since V(B) need to be forced by extra circuits. Goal is making these voltages as close as practical so VDS modulation error will be small.

Answer to 2: You are right. N2 needs to be in saturation. N1 is forced in saturation as you said sice gate and drain shorted but N2's operation mode is forced through N1. If N1 is not sized right to begin with N2 will not be in saturation. If N1 and N2 are the same size, N2 is in saturation and V(A)=V(B) than N2 copies the current of N1.

Answer to 3: This is for any individual transistorI =K(W/L)(Vgs-Vt)*(Vgs-Vt)= K(W/L)*VDsat*VDsatSo chosing Vdsat~200mV (I/(W/L))= current density =K(VDsat*VDsat)=constant. Therefore for a desired current there is a corresponding W/L value for a given process. For a mirror with equal size transistors both N1 and N2 will have the same current density. Good luck.

回答:这是一个错字。是的,你明白它的权利,对于所需的额定电流(以及围绕它所需电流范围),我们希望电流镜晶体管在饱和区。 N1和N2有一个比较大的~200mV的VDSAT和 V(A)= V(B)。由于晶体管栅极和源是常见的漏电压等于设置的两个晶体管的工作条件是完全平等的,所以电流将完全复制(内由于不匹配等实际限制)。现在使 V(A)= v(B)是在实践中很难的,因为V(b)需要额外的电路被强迫。目标是使这些电压,如实际接近VDS的调制误差会小。

回答2:你说得对。 N2的需要是处于饱和状态。 N1是被迫处于饱和状态,如你所说SICE门和漏极短路,但氮气的运作模式是通过N1的被迫。如果大小的权利开始与N2 N1是不是会不饱和。如果N1和N2是相同的大小,N2饱和度和 V(A)= V(B)比氮气复制N1的电流。

回答3:这是任何单个的晶体管是我= K(下的W / L)(VGS-VT)*(VGS-VT)= K(下的W / L)* VDSAT* VDSAT所以VDSAT艇员选拔~200mV的(我/(宽/ L),)=电流密度= K(下VDSAT* VDSAT)=常数。因此,所需的电流有一个相应的W / L值给定的进程。对于与同等大小的晶体管的一面镜子,N1和N2都将有相同的电流密度。祝你好运。

如果 mos current mirror 要準,L 變大下

你要達到同電流大小下 W 就是得變大 .

有事最近几天没上论坛,很抱歉,非常感谢您的回复。此贴的问题您给的帮助非常有用,再次感谢您。

感谢回复。

L和W都要大点,这是电流镜的一般要求,不知道我理解您的意思对不对?