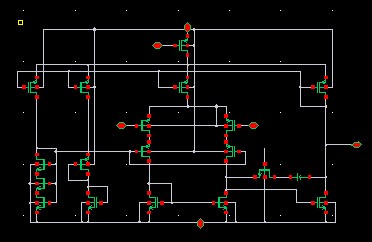

运放输入管工作在线性区是为了什么

自己顶起...

看起来输出做自偏置,目的是加快启动,电路用在什么上面的?确定是个运放么?真是运放的话输出摆幅也太小了!

这个主要是用作基准后面的缓冲级的...这样接仅仅是为了加快启动速度么? 那输入管工作在线性区又是为了什么?

再顶起...

求助中....

你这个电路能启动吗

不太可能是线性区,是否直流偏置不对

等大神,电路没看懂

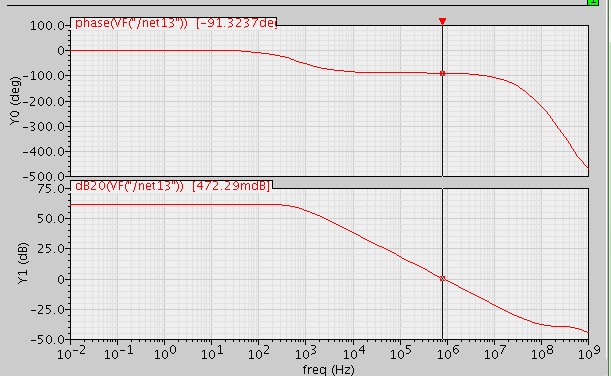

刚刚又看了一下...输入的两个管的确是偏置在线性区的...在整体电路里这个运放充当单位增益的缓冲器,负反馈接回来的偏置也是使那两个管子偏置在线性区..下图是其幅频特性..相位裕度留这么是因为后面还要接一级,考虑到稳定因素...但是这个工作在线性区的管子画layout的时候很容易因为寄生导致增益变化很大...所以一直不理解...还有后面把输出用来偏置尾电流又是为什么呢?是用来加快启动的么?我觉得不大像..

启动这边有专门的启动电路来处理...这个只是基准输出的一个缓冲运放,应该不需要专门的启动吧?

自偏置在bandgap里挺常见的,不明白bandgap buffer为什么要这么做,看不出好处在哪里。

另外输入级在线性区,撸主确定不是设计的问题?

1.输入级见过亚阈区的(低功耗),线性区悬吧!业界不会用吧!

2.为什么用输出端来偏置输入级地尾电流源,输出在变呀!那输入跨导总在变?这是什么呀?

好多不理解。

自偏置是因为使得基准可以在偏置电流模块起来前工作?

如果是Buffer连接,输出端接一个输入端,输出直流是VDD-VGS,很明显,此时直流值不可能让输入管工作在线性区。具体应用电路可以给出来么?

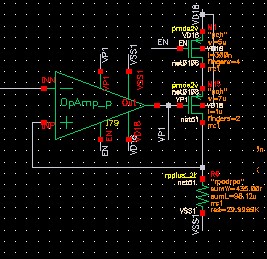

嗯..buffer部分的图如下,输入的是经过分压的基准电压...这边不是直接从运放输出接回去的,所以不是VDD-VGS...Vp1就是用来给自己为电流提供偏置同时给其他运放也提供偏置的...我也怀疑输入管工作在线性可能有问题...还有就是这样给尾电流偏置有什么优点么?有没有类似结构的文章?

这个是曾经的一位师兄做的..因为要拿去流片...所以检查了一下....我也是觉得这两个地方有些问题...最好能有文章之类的提到这两个方面的...

我觉得吧不如你自己再做一个,也就是半天的时间而已。你师兄做的不见得就是好的。运放输入端偏置在线性区本来就是挺匪夷所思的。自偏置感觉也是问题多多,尤其是上电的时候。

按照这种偏置接法,输入管有可能在线性区,使得增益的线性度得到提高。

提高增益线性度?能具体解释一下么?谢谢

不是线性区,是饱和区。

另外也不能简单的看成是输出驱动,这是个二级运放(后一级是共源级),你第一级的输出不接第二级的输入怎么能行呢?相邻的那条只是米勒补偿。

不过你共源级的负载管是不是接错了呀?要接二极管形式,为什么还要偏置呢?要偏置电流源形式为什么还要接成二极管形式呢?

这里说的线性区是差分运放那两个输入管处于线性区...那个共源级负载接成二极管形式是来偏置差分管的尾电流的...不然尾电流这边就没偏置了...具体原因我最近还是没找到相应的文章..

请大神正解!