这个开关要怎么分析?

时间:10-02

整理:3721RD

点击:

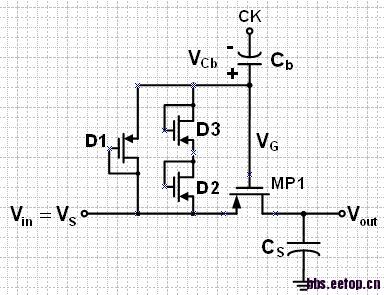

CK是0~5V之间的clock,Vin<1V,MP1做开关,我是这样分析的:

想问下我这种分析的状态存在吗?还有这种开关和普通的Bootstrapped Switch相比有什么优缺点?

CK上升沿时,D1on,电容Cb放电,MP1截止,CK下降沿时,D2,D3导通,电容Cb充电,充电电压被D2D3箝位,MP1导通.

问题就在这个地方,CK上升沿时,D1为什么一定是导通?为什么就不会是关断?

假如Cb上存在初始电压的话D1有可能关断的啊

D1上升沿时,电容两端电压差不会突变,电容下极板电压为5V,则上极板电压相应增加5V,这个电压足够D1导通了

谢谢您再次回复

会不会电路刚启动时Cb上已经带电压“-5v”,然后如您所说上极板电压相应增加5V后变为0v,D1仍关断?

即使启动时CB上有负电压,这只会影响第一个时钟周期电压的输出,以后的时钟则按前述分析。

多谢多谢,仔细看了下是我自己算错了

我看了下这个电路,给出自己的分析,有不足的地方请指正。

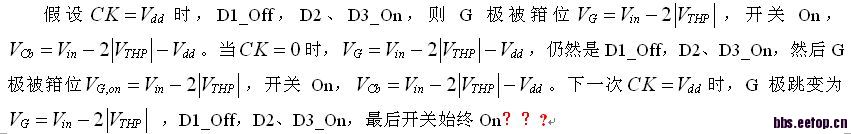

在上电前,电容Cb是不带电的。当第一个时钟上升沿到来时,电容上的电荷由于不能发生突变,所以电容上下极板的电压都为5V,这时D1导通,D2和D3关断,这时电容放电,最终电容上极板的电位被嵌在Vin+|Vthp|,显然MP1管关断。当时钟下降沿到来时,这时同样电容上的电荷由于不能发生突变,所以电容的下极板的电压为Vin+|Vthp|-5,这时D1关断,D2和D3导通,这时电容充电,最终电容上极板的电位被嵌在Vin-2|VthP|,这时的Mp1管导通,并且具有恒定的过驱动电压|Vthp|

这种结构适合PMOS管做开关,结构相对简洁,但相对于同样大小的NMOS管,没有啥优势。