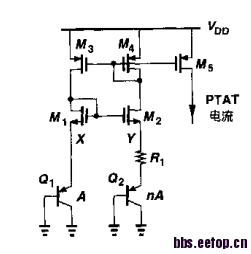

设计PTAT时,corner的影响是不是很大?

结构图

,

,tt时的电流是20uA,可在ff:24.5uA,ss:16uA。

感觉偏差很大啊,

这样的结果是否合理?

谢谢

有几个原因:

1。回路的gain过小,因此across corner时造成offset,导致PTAT变化,这个可以从DCOP看出来

2。看看model里面ff到底变咯什么,是否已经包括BJT的变化。

3。输出的current mirror rds 不够,稍微一变化corner就会导致current 变化

谢谢你的关注以及回复,

我会针对你的这几个原因进行验证,另外ff是fast的model,包括res和bjt

多大是指多大?1%的变化是很正常的。

昨天看还是如题,今天配上图了么,呵呵

不算温度变化, 这个variation 就是电阻的 corner variation

+/- 20%就是corner定义的值

谢谢回复 那照这么说的话,PTAT中的电阻类型应该选取corner变化最小的,而不一定非要用具有负温度系数的高阻poly?

观察这个电路,首先,你的电路必须匹配好,尽量防止sys offset, 减少random offset那么过corner的时候,假设两条之路电路电流相等,那么,(vbeL-vbeR)/r 在Ic相等的情况下,分是不会有大的变化 (bjt面积一样)。那么此时,看电阻的变化,通常+-10%。自己推。

明显是设计的不好,只要保证X和Y两路的电流一样大,这个电路才是合格的。

把匹配管的尺寸做大点!

我第一次做这种结构的bandgap的时候

各个corner输出电压的温度特性都能维持在10ppm之内。

如果是运放结构的可以优化到5ppm。

公式可以帮你更好的理解bandgap

同时还要仿真确定bjt的指数区间

一般VBE在0.6到0.7伏特之间比较好。

楼上注意了,小编说的是电流

这个电路我在用90nm做的时候,性能不怎么好,特别是PSRR。当然我的vdd也低。