LDO稳定性仿真问题

iprobe加在buffer的输出端

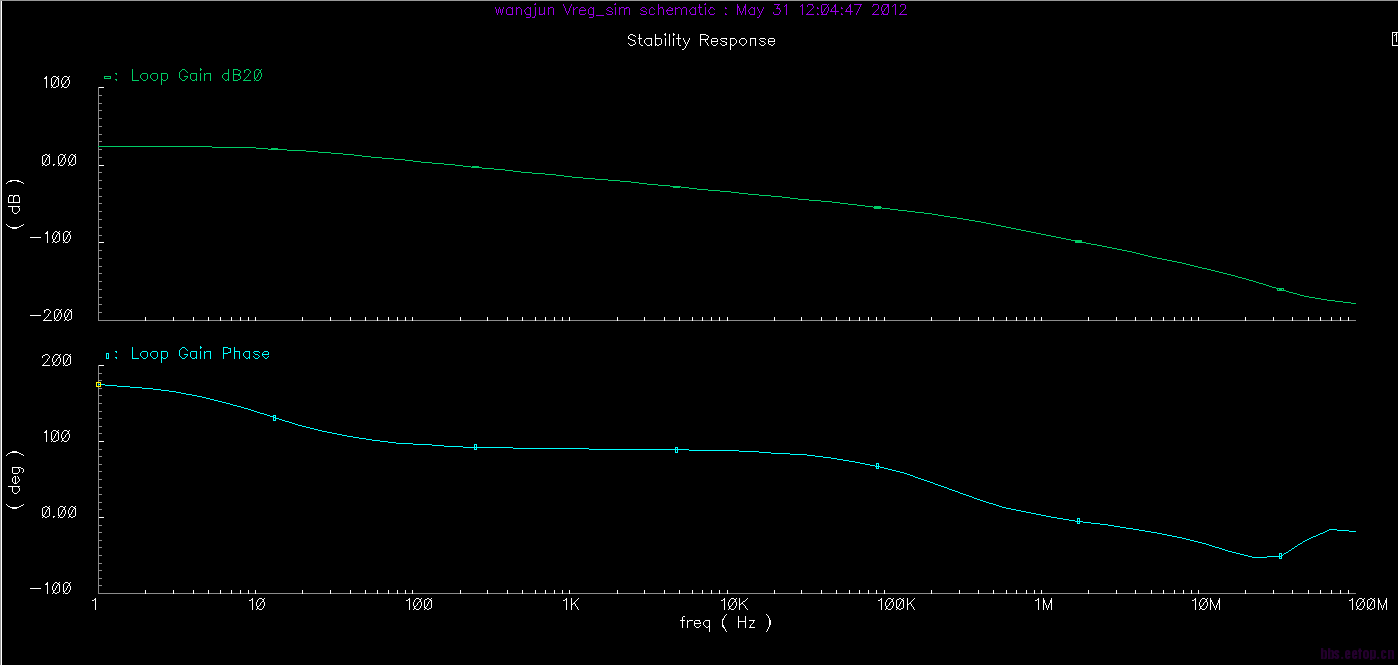

stb的仿真结果是PM 93Frequance 100Hz

Gain margin 92dBFrequance 1.1MHz

loop gain波形图

相位裕度93应该稳定的,但是网上说增益裕度是指相位达到-180时的增益,那时的增益不是应该小于0了吗,为什么92dB呢

谢谢大家帮我分析一下。

这个结果已经非常稳定了吧。

对于你所说的增益裕度的问题,phase达到-180时,增益为-92dB,GM就是92dB了。

哦,谢谢。这个问题我明白了。还有就是对一个LDO而言低频环路增益只有25dB够吗,我的运放单独仿有60dB左右增益的

运放的增益主要影响输出电压的精度,看你的SPEC是什么要求了。

为什么你的环路增益这么小呢?是不是反馈电阻取的太小了?

不好意思看错了,你的电路有buffer,增益跟反馈电阻大小几乎没有关系。我感觉你对仿真的理解有问题,单仿运放你是怎么仿的?开环?

不知道啊,我看其他人的环路增益都有几十的,我再研究下一下吧,谢谢你了。

谢谢,单独仿真就是运放开环仿真的,想仿的差不多了就拿到闭环里仿真试试,是不是这样仿真有点问题?还有环路增益低刚刚我找到问题了,buffer那里有点问题把输出低静态点降得太低了,放大器的输出管有一个进入线性区了,我已经调好了,现在仿真低频环路增益能达到48dB了。现在问题就是GBW太低了(13kHz主要因为输出处有个1uf的负载电容),我要用这个LDO做电源,后面还要接1MHz振荡器什么,可能高频噪声很严重,想增大GBW是不是唯一的办法就是增大放大器的gm?那样的话静态电流会很大的。

开环仿真没有多大意思,除非做比较器。

GBW跟你的运放结构有关系,如果是主极点在输出端的,负载电容就会有影响;如果主极点在电路内部的,比如两级运放+米勒补偿,主极点主要是米勒电容决定。

你现在的情况是负载电容太大了,主极点频率很低,想增大GBW只有增大gm了吧。

恩,谢谢你了。我觉得只有增加运放gm了。

这是带负载条件下的PM吗? 如果是,那很好啊

相位裕度就是在交流开环下的定义,不可能闭环仿真,大家看到的闭环形式是直流反馈的闭环,很多人这个问题概念混淆。

我明白你的意思,开环、闭环、环路,是三个概念,虽然现在是闭环,但是加入了iprobe,所以等于把闭环打开了,仿真的是环路增益GBW和开环下的GBW应该是一样的。之所以这样仿真是因为单纯的开环仿真无法获得最直接的信息,这样仿真就能把负载环境什么的都考虑进去。