问个很搞的问题

具体电路就是常见的经典电路如图所示,为了实现我先前说的,我现在是倒过来,把二极管接法的MOS的W/L做得比三端接法的MOS的大了,大家看看我这样子干会有什么问题吗?

就没有迟滞功能了

这么做就没有hysteresis了

原理比较简单,建议手动推导一下,理解为什么没有迟滞功能了。

只有自己推导+仿真才能理解原理

按照推导,如果M6 M7的尺寸比M3 M4大,才会有迟滞。

ps:反过来做也是有用的,历史上在Harold Black提出负反馈放大器(Razavi的著作中也有提到此人哦)之前,designer们为改善通信电路中的讯号衰减,而用正反馈来实现放大器的gain boost,这是因为闭环增益=开环增益/(1+LG)中的LG如果为负(positive FB)且绝对值小于1,那么闭环增益将超过开环增益,这个概念在五六十年代的电路应用中非常常见。因此,你做反的结果,是得到一个增益更大的比较器了,不信你可以simulate试试,看看你比较器的分辨率是否会有提高。

来算算

尺寸比例反过来做,输出阻抗很大,增益就高,在比较器的pre-amp里经常有人这么做

我知道没有迟滞,我就想知道这样有没有什么坏处?我这是作为整个比较器的第一级pre-amp用的,使用输出失调存储,不闭环。vinp-vinn是锯齿波,不会长时间落在已经‘不是迟滞’的两个翻转电压之内。落在之内时是不是抗干扰能力会比较差啊?

其实这是比较器的第一级做pre-amp用的,比较器使用‘输出失调存储’。但是因为输入压差是个锯齿波,不会长时间落在两个翻转电平之间的

我仿tran验证过了,增益没有很高啊(不是gmRds这个级别,只是20dB左右级别)?是不是我要加些失配或者其它非理想因素进去?我比较急啊,如果真是很大就不能用输出失调存储,如果你确定是很大,麻烦讲解下怎么回事好吗?

学习了,以前以为接成这样的比较器都是有hysteresis的。

输出阻抗是2/(gm3-gm6),如果gm3略大于gm6,输出阻抗就有无穷大的趋势,也看你的设计,如果m3尺寸远大于m6,那增益就不高了

理论上增益会比较高

吓死我……我是不会让他们尺寸相等的,那就应该没有问题了,多谢大侠!

能否想再问您一个问题,像这样的pre-amp的传递函数从迟滞的变成了有缺口的,没有什么别的缺点吗?另外我用的是输出失调存储,所以是开环使用的,和5# 所说的闭环使用还不一样,不知您所见过的pre-amp是用在输出失调存储里的吗?

缺口是啥意思?这种pre-amp在pipeline里有见到用过的,尤其是2-3bit/stage的pipeline,对offset要求高一点的

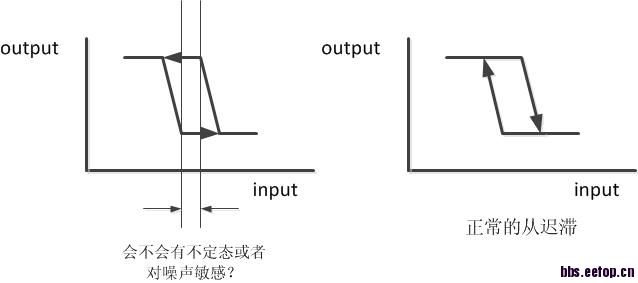

就是像图中左边这样,右边的是真正的迟滞。我就怕中间这段容易出现不定态什么的

Metastable state吧,ADC里貌似很少有讨论这个话题的,可能不是很重要吧