高带宽,大摆幅,小电阻负载可行性分析求助

时间:10-02

整理:3721RD

点击:

路过的各位大侠请帮忙分析下,基于CMOS工艺设计如下SPEC是否有可行性,有无架构推荐呢^_^

具体指标如下所示:

工艺:CMOS

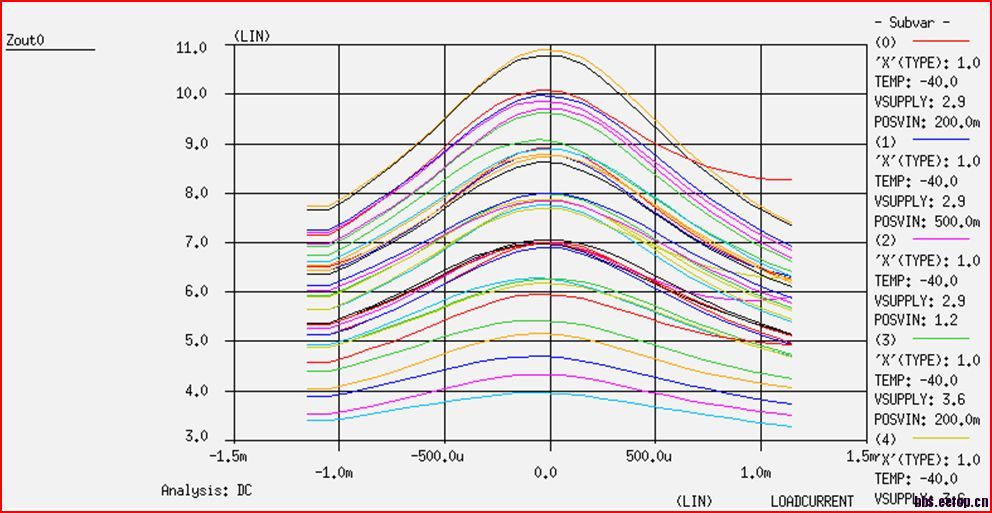

负载:50 OHm,1pF

单端输出幅度:2.5Vpp

电源电压:3-3.3-3.6V

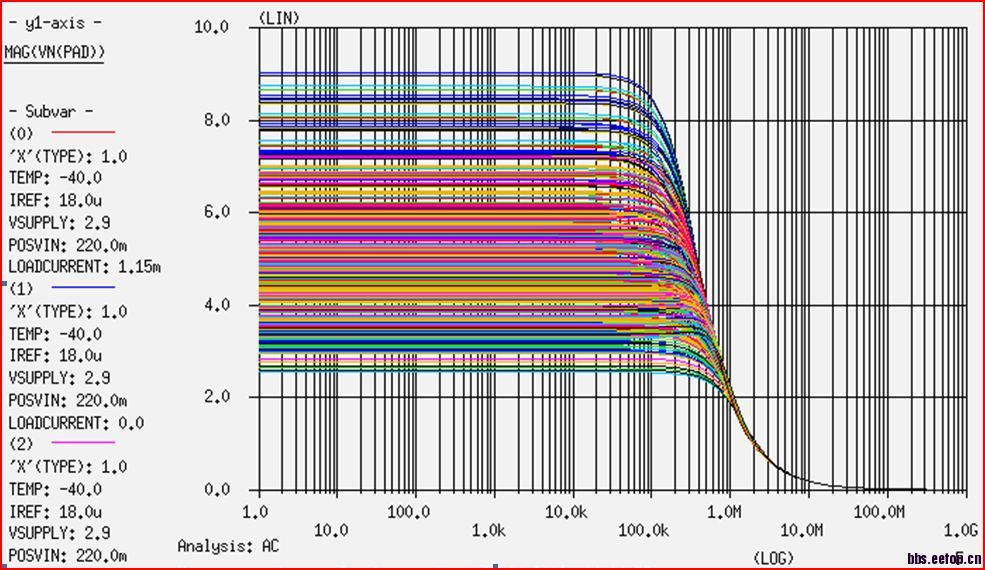

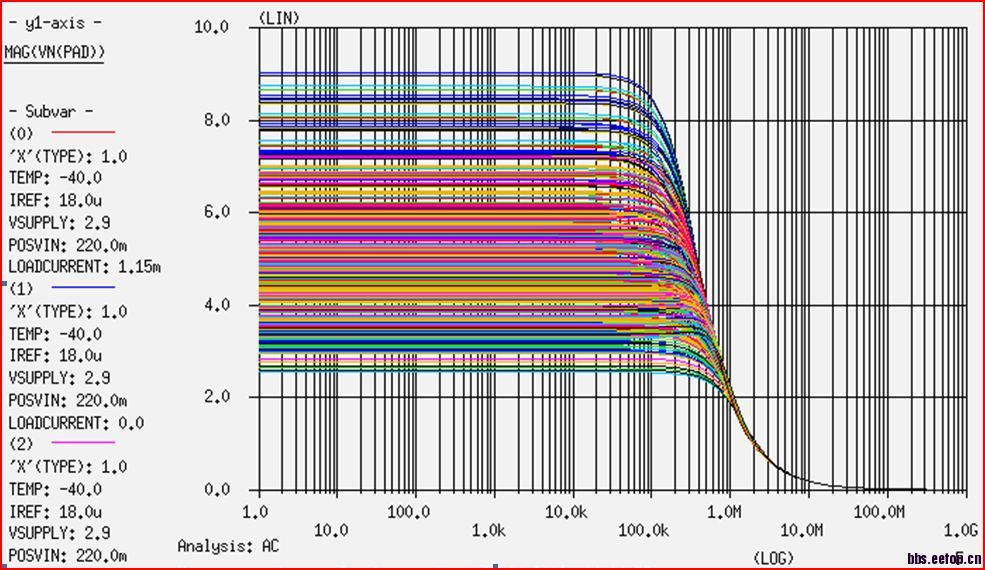

增益:12dB+-0.1dB(100MHz范围内)

-3dB带宽:大于200MHz

THD:45dB@60MHz

功耗,面积暂无要求。

谢谢。

具体指标如下所示:

工艺:CMOS

负载:50 OHm,1pF

单端输出幅度:2.5Vpp

电源电压:3-3.3-3.6V

增益:12dB+-0.1dB(100MHz范围内)

-3dB带宽:大于200MHz

THD:45dB@60MHz

功耗,面积暂无要求。

谢谢。

你要做啥?

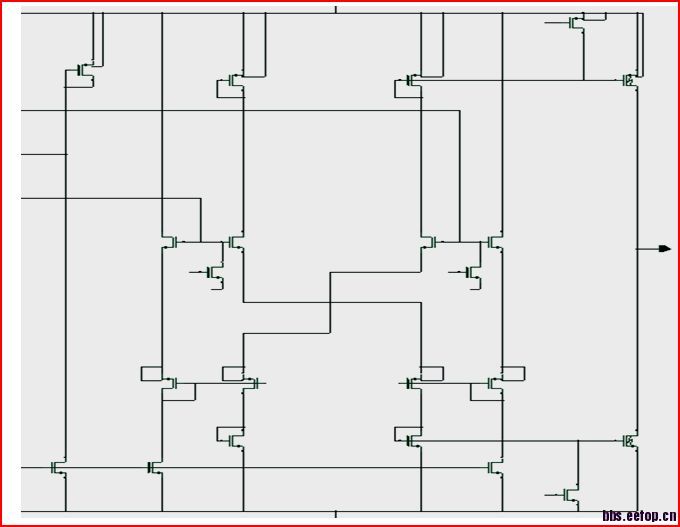

就用classAB 输出级就好了,输出电阻可以做到很小,1-2欧姆。

做一个固定增益的Driver

Class AB 前一级如何驱动,如果做到高带宽呢,还请指教,谢谢

ClassAB的偏置是设计classAB本身就需要解决的问题。至于高带宽,只能用gm驱动交流等效阻抗不太大的负载来实现,那么就可以实现高带宽。应该不难吧。

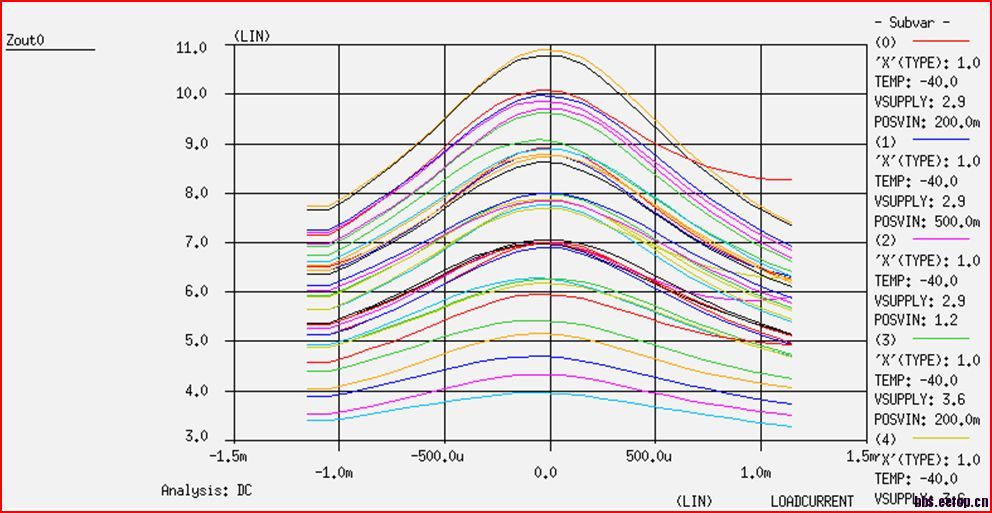

有源级跟随 负责diode负载驱动最后一级,目前评估的结果是最后一级的栅寄生电阻有几十pF,那么导致前一级的节点阻抗要至少小于100 Ohm,而这又会导致源跟随要做得比较大,寄生有上来了。

不知道您是有能画一个大致结构图上来呢?谢谢

我很多年前做过一个ClassAB输出, 输出阻抗控制在10欧姆以下.

谢谢啦,我先研究研究先,

冒昧问下,前辈在那高就呢^_^

我要是敢自认是前辈那一定是在冒充.

谢谢啦,在class AB这方面,您肯定是我的前辈呢^_^

小电阻负载肯定得用class AB结构了,这个specs咋一看不算太难