为什么ADC测试结果是7次9次谐波高?

时间:10-02

整理:3721RD

点击:

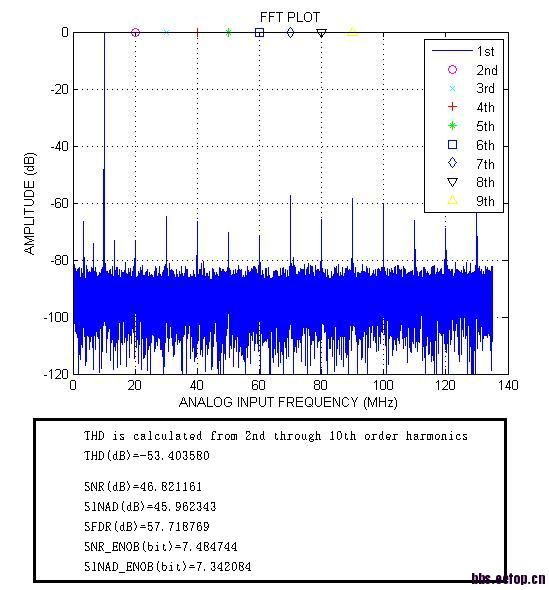

贴一下测试结果的FFT。

请高手帮我看看。

对了 我这个ADC是单端输入的,前面有单端转差分电路和PGA电路。

ADC test

matlab跑的行为级还是?

不像是测出来的,像是仿真结果

可能:数据卡采集,MATLAB分析

说说信号频率,采样频率。

另外既然是测试,就测测谐波对信号的幅度以及频率的关系。

只有多收集些信息才能知道问题出在哪里。

现在这样就一个测试结果,有多种可能性。

是真实芯片的测试结果。逻辑分析仪的采样数据用matlab处理的。

采样时钟270MHz,输入信号单端的10MHz,信号源加了带通滤波器。

按理说最差的应该是3次谐波最高,为什么是7次和9次谐波最高?

还有很多其他的结果,和这个差不多。

不是仿真结果。是测试结果

仿真结果(后防)SFDR70dB以上。

差分输入SFDR80dB以上。

准确的10M?如果你说信号频率变化一些也没影响,那就排除量化造成的问题,否则没法排除是量化引入的问题。

不是准确的10M,9.9999M之类的吧,能保证非相干采样。

示波器看信号源波形也很烂,但是没有频谱仪看信号源SNR到底能到多少。

这明显是测试结果,这个最起码32768点dft做出来的

电路仿真能做到1024点就谢天谢地了,时间太长,忍不了的

你把clk频率降下来,再测一下,我做160M的时候噪底起来,但不是在谐波上,但是间隔比较固定

分频就好了,怀疑clk有问题

不要用示波器看信号源,示波器才8bit ADC

什么牌子的信号源,agilent的应该没有问题

这个matlab 程序好熟悉啊,哈哈

270MHz的ADC 是为video AFE 做的吗?建议先测测低频clock的,甚至低频输入的性能。一步一步来,有些问题还是比较一下能找到root cause