如何才能避免启动电路给基准充电(或者)放电?

时间:10-02

整理:3721RD

点击:

题目中说的就是“和VCC无关的基准”,而非BG

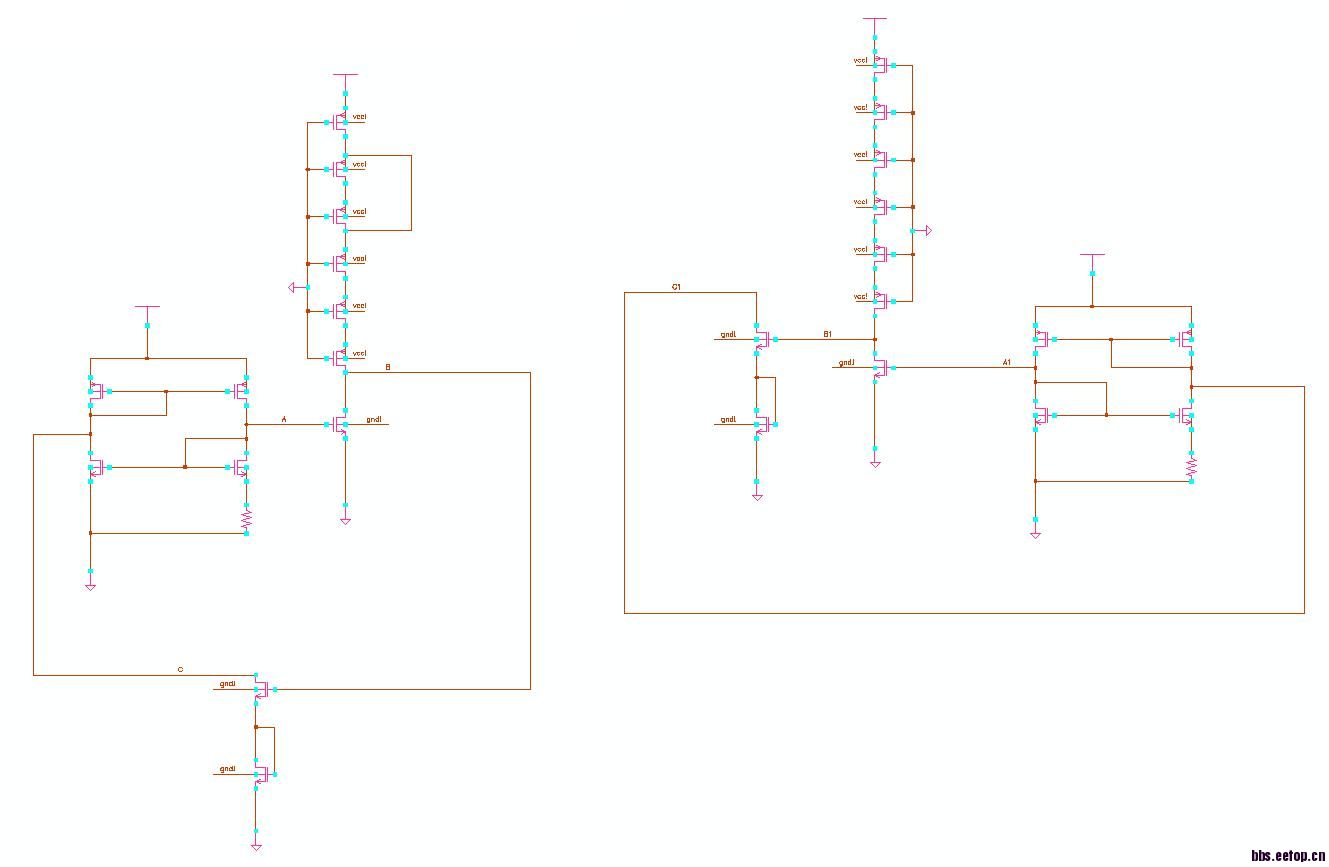

如图所示,左右两个电路结构基本上是一样的,只是基准镜像的方向刚好相反

带负反馈的NMOS的W/L设置不同,以避免环路不稳定(左方电路类似的结构出现在拉扎维的图11.3b中,因此肯定是可以使用的结构)

但是以仿真结果来看,右边的电路能够正常启动,左边电路则是:启动的NMOS泄放掉大部分基准中的电流,C点电位不是很低,A点不是很高,B点也不很低,使启动电路稳定在一种中间态

(右边的基准结构,以前也有人出现过类似的问题,因此应该和基准本身的结构无关)

两个电路的本质区别就是source degeneration 的电阻位置不同吧。右边的电路可以做到source degeneration后输出阻抗增加,环路增益也足够大。左边的电阻放置在diode下面,输出阻抗会是多少?环路增益好像也没有多少。但是这个电路也不是完全不工作的。所以你看到的是一个不想要的中间态?

这个环路应该是正反馈,左边环路增益大于一,右边小于一,右边可以到正常的工作点

很有可能是拉扎维书上的那个11.3(b)画错了,我怎么看那个图环路增益都大于1,这怎么可能能稳定啊 ,拉扎维那个图的初衷吧rs放左边就对了,也消除了体效应,也能使恒跨到源稳定