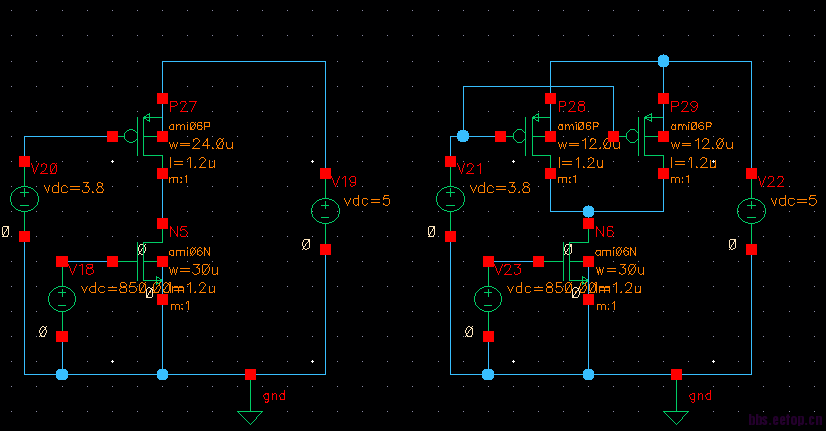

请教一个基本电路问题,比较这两个电路

这两个电路中的pmos和nmos所加的偏置电压相同,vdd相同。nmos的尺寸相同(30/1.2),唯一的区别是第一个图中是单个pmos(24/1.2),第二个图中是两个并联的pmos,尺寸减半(12/1.2)。

请问两图中的电压和电流有何不同,为什么?

没啥不同

24/1.2与2x12/1.2相比,在尺寸上没有不同。但是现在的MOS管的model是按照W、L的尺寸划分拟合区间的,大多数工艺的Model在W=20um的时候是个分界线,大于这个尺寸和小于这个尺寸用的是不同的model。

所以我估计这个电路的电流有可能不同,如果不同的话,就是model的问题。

谢谢,不过我发现我用的model好像在小尺寸的情况下,这两个电路仍然有不同,只不过差距小一点而已。

单从公式上分析,

两者应该是一样的。

请问前辈,model上的差别主要是由于什么造成的呢?从工艺,物理层怎么理解?

和物理版图的形状以及寄生有关(这样就影响了模型),一般对直流点没有影响,交流有一些影响

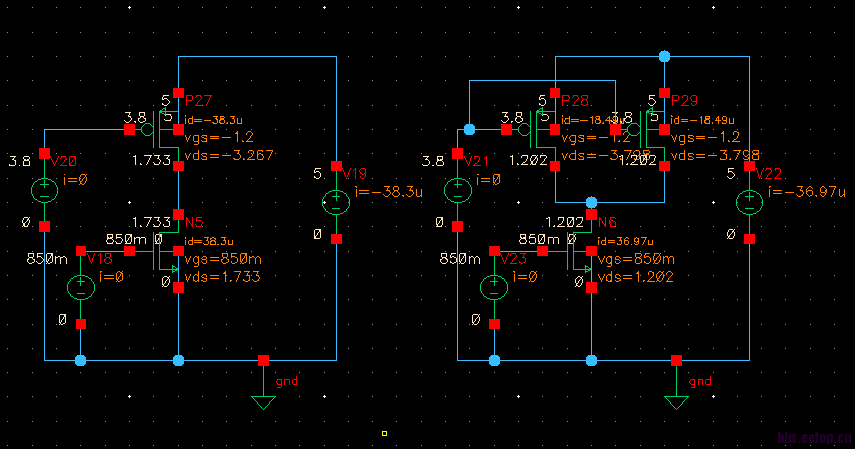

再附上一张DC工作点的图

望各位大牛指点迷津啊!

Did you check the Vth of each case? If the model includes some layout effect (e.g. LOD effect), then the vth can be slightly different and hence the DC performance. Just my guess.

学习中。

仿真结果的不同主要取决于layout的不同,在sechmatic中有一些switch选项是关于layout的效应的(STI、阱临近效应)等,这样就会使仿真结果不同。

其实我们学习的那种模型是最最简略的模型,它的主要任务是让我们通过手算达到对电路的理解。而MOS管本身是很复杂的,想BSIM3v3是个场模型,我们从里面根本不会找到你说的公式。BSIM3v3想通过划分不同的w、l区域让model与MOS管的物理特性更加吻合,如此而已。但是,模型就是模型,他绝对不可能完全吻合物理现象。这个才是真理。

你说的小尺寸下还是和手算的不大相同是可以理解的,如果你想知道得更多,建议你读一些model的书籍就了解更多了。简单一点的话,你就打印一下直流工作点,什么Vth啊、u0啊,应该都有轻微差别的。

图一图二中的PMOS应该是工作在不同工作区……LZ check一下吧.

lamda不同,电流也不同,ro不同,还有sidewall之类的电容也不一样,因素太多

wind2000sp3正解,如果有pre-sim的话,一些寄生参数也会不同

拉扎维那本书里面说 WL大了可以减小各项失配

是不是这个原因呢...

vth 确实有微小的差别,不过这也是正常的,不至于对电路有这么大的影响吧.

在这两个图里,他们都是饱和的,你看一下vds和vgs就知道了

对,我做这个的就是为了仿真schematic和layout的区别,在这个电路中0.5v可能还没什么.

可我做的一个3级放大器schematic跑的好好的.画完版图仿了一下提取的网表,结果第三级就不饱和了.感觉很奇怪,觉得差别有点太大了

我想知道为什么lamda是不同的,W不同,但L都是一样的,Leff不也应该是一样的么?

说得太好了,我先找本modeling的书看看.

不过先说一下我遇到问题吧:

设计了一个三级运放,schematic仿真结果挺好,画了一个layout,仿extracted,结果没有增益了,检查了电路节点,发现工作点跑偏了,原因是fingers造成的,于是反过来仿了一个基本的schematic(如上图),发现原来model本身就是这样的,觉得很郁闷,不知道为什么会这样?

不太可能是这个导致得

那是为什么呢?请高人指点.我的layout应该没问题,LVS,DRC都过了.提取的寄生参数只包含电容

后面的一个电流大点,区别不大

If you have problems in post-layout sim, then check the WPE effect. It is not uncommon for the Vth to increase by 0.2V just due to WPE effect alone. Keep enough spacing between your transistors and N-Well, OD2, etc.. DRC and LVS clean does not mean everything.

w=24与两个w=12并联本来就并不一样,前仿都有差异,不用后仿参数去说明什么。

w=12 m=2才等效于两个w=12的并联。

其实这就是所谓后仿真的重要性!

即使schematic做的再好,它和后仿还是有差别的,甚至很大差别!因为post-layout,包含了很多的寄生效应,诸如电容、电阻,阱临近(WPE)效应、STI等等。

你可以做个试验,同样的schematic,画几个不同的layout,看看这些layout的后仿结果是否相同。

应该是有差别的。

今天meeting boss让我们重新设计schematic,把管子的size改成m的值和layout的叉指数目相等,说就算不相同,也至少是估计近似.这我就纳闷了.

恕我无知,在实际电路设计中(先不考虑版图),也是给出一个考虑叉指数?还是直接给W/L然后算? schematic和layout design应该不是一拨人吧?

另外,前辈你说的关于不同layout的问题,在叉指数目相同的情况下,不同的layout提取出的网表是不是只有电容值是不同的?如果只有电容不同,那是不是不会影响DC工作点的问题?

我知道后两个是一样的,我就是想问一下,为什么前两个不一样?

可能是我的版图画得不够好.没怎么考虑WPE effect. 你说这个对fabrication有影响,我觉得没错. 不过我也不觉得extracted会因为n-well的大小不同会有多大的变化

对你的两个问题的回答:

1.电路设计中应该是先给出W/L,在拆成不同的finger,甚至有时候finger数是根据layout的实际情况改变的。

2.不同layout不仅是提取的电容、电阻值的区别,其他效应的区别有时更甚。你可以试一下同一个layout,放置不同的device距离、连线宽度、VIA个数、dummy器件尺寸&个数。,它们的后仿结果是有区别的,即使和你的schematic都是lvs match的。

lixiaojun707