设计了一个CT SDM

时间:10-02

整理:3721RD

点击:

现在正设计一个CTSDM,采样频率160MHz,带宽4MHz,采用了单环3阶4位结构,现在matlab仿真没问题了,但将参数带到实际电路,运放输出却出现了饱和,其中,参考为600mV,输入峰峰值为100mV。同时,电路中,AD用VerilogA模型。运放的GBW为340MHz,增益为66dB。估计问题出在反馈DAC,而DAC我用的是15个current steering DAC cell。大伙帮忙分析下问题出在哪?谢谢

就凭现在这些信息就看出问题在哪里的人估计不多,或者说根本没有,因为可能原因实在太多了,真想请教,得先把问题解释清楚

你三阶用的同样的opamp? 另外单环三阶4位,不知到你的snr和sqnr要求是不少,4mhz的带宽?确定不是dac delay导致阶数变大?

问题已解决。AD的转换时间过长了。在模型里改了就好了,谢谢大家关心。

thank you

DINGDING

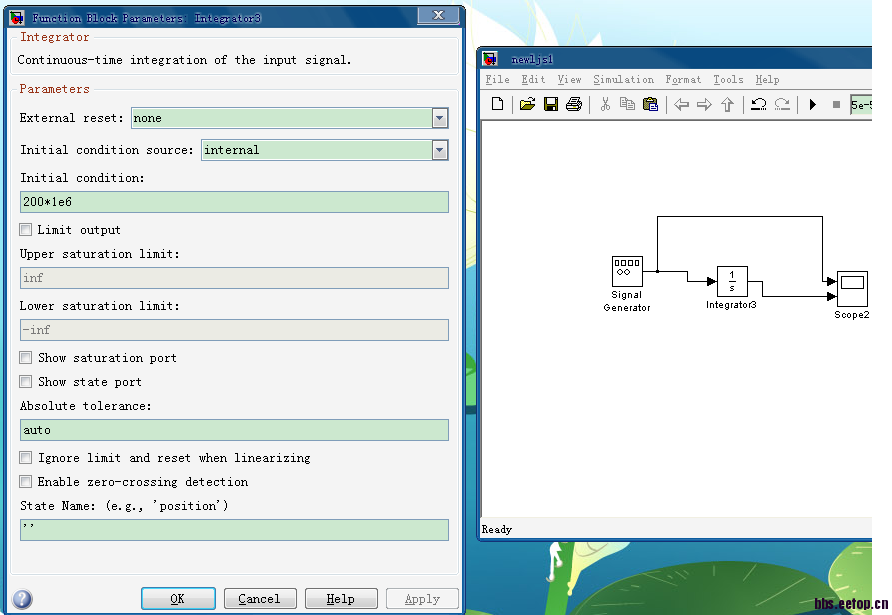

你好,我是sigma delta的初学者,我要做一个连续时间的sigma delta,可是在用matlab建模时,积分器1/s的输出不正常,幅值几乎为0了,您知道是什么原因吗?是我积分器1/s参数设置不对的问题吗?我在eetop上了解到您已经做过一版连续时间的sigma delta了,所以特来请教一下,

把1/S改成fs/S应该可以正常

谢谢了,我试试看

fs/S中fs不是采样时间吗?simulink建模里这是需要给值的啊,是给我设计的值吗?可是我按自己设计的数值给1e-7,仿真结果还是几乎为0啊,是我理解错 了吗?

simulink中连续时间采样值设为0,离散时间设采样时间。你用s=j*2*pi*f代一下,你的积分器增益是多少。真实的积分器表达式是omigac/s.

积分器模型没错,它的传输函数是1/s;如果输入频率是f,则输出幅度为1/(2*pi*f)。如果你的输入频率比较高,输出幅度自然很小,是对的。实际应用中你可能还要乘个系数什么的以得到你需求的传输函数。

谢谢,看来我的matlab和sigma delta了解的都还不够啊