哪种power down的方式更好些?

时间:10-02

整理:3721RD

点击:

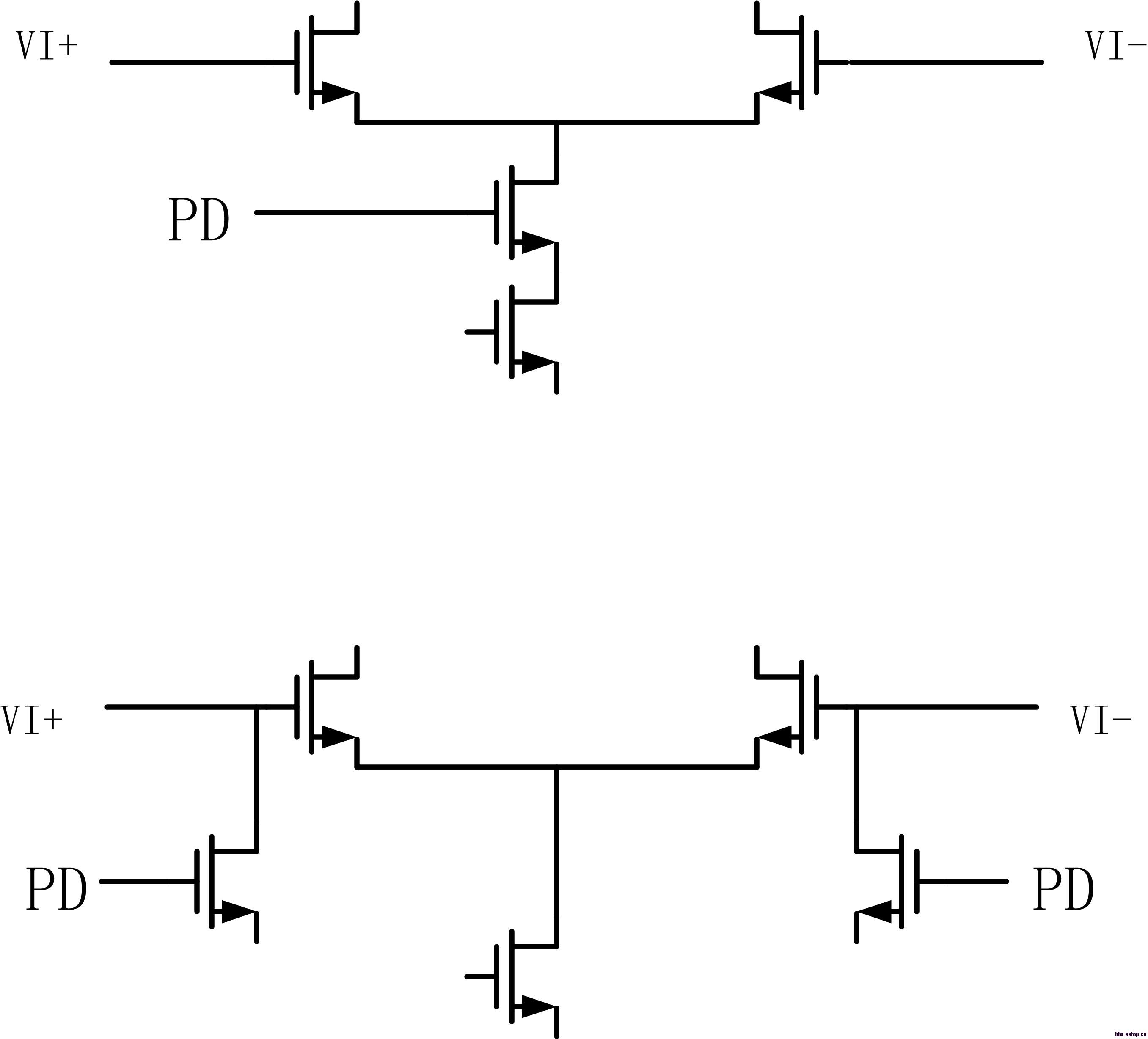

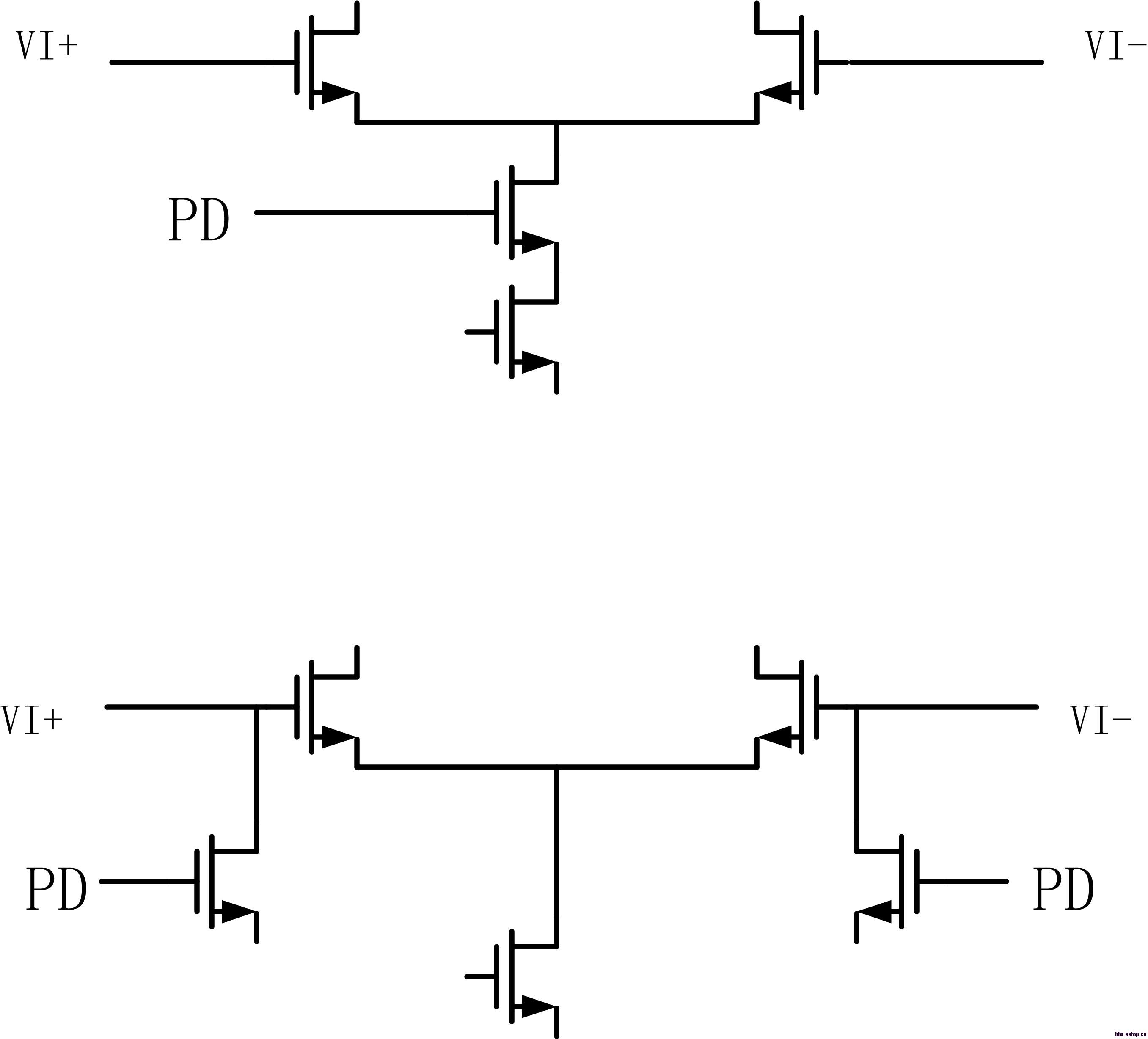

因为是AD里用的,需要从信号完整性上细致考虑。经典的5管运放,以下只画出输入对管和尾电流部分,那种更好些呢?先谢谢大家啦!

power down bias current source

tie low the the gate of NMOS in current tail branch

我也知道这样可以,但是我是有若干个电路公用这个bias电压,要shutdown就都shutdown了。鉴于我的具体方案,我是不可能每个电路分配独立的bias电压的。所以可选的应该就我图中的两种

第一种是更合适的。

一般Power down先是关断偏置,这样耗电少、速度快!

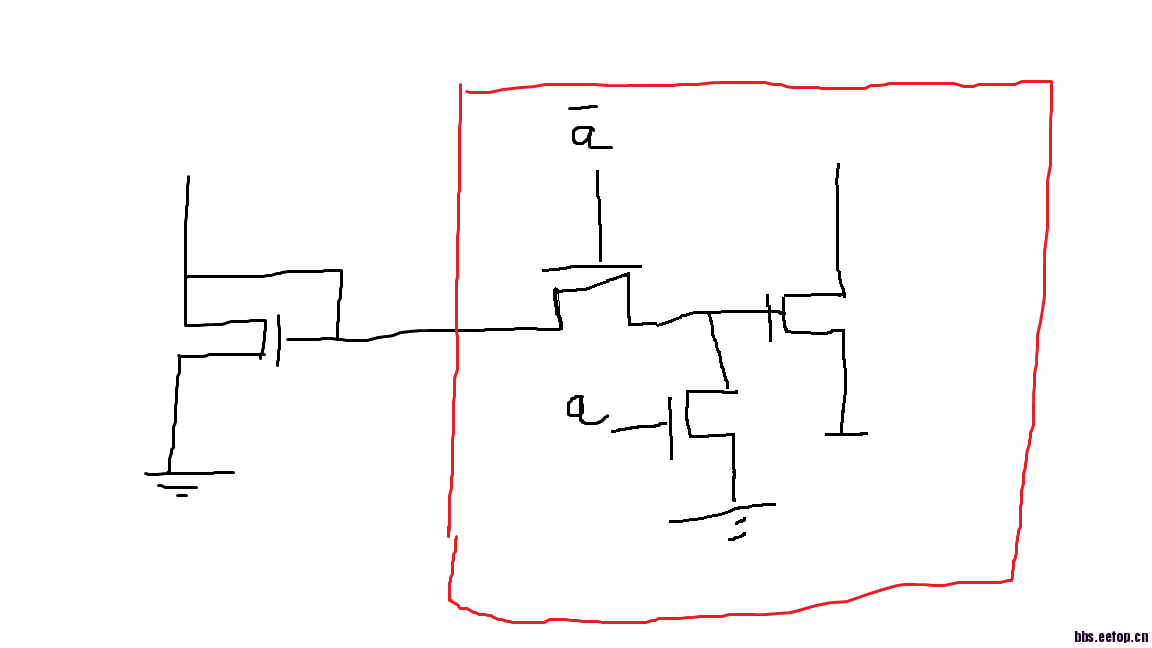

you can use nmos as a switch which serie with the gate of tail device. The tie low device can be put in internal side which will not affect your power down function.

你说的对

使用NMOS作为开关,连接到尾电流器件的栅极。

拜托,我在3#都说了,我不可能把尾电流栅极拉低,这个栅极被好多个电路共享的,一拉全都拉低了。我的电路比较特殊,我也不会每个电路分配一个偏置电压

不过还是多谢回复!

你不能在这个栅上串个开关nmos啊,开关外接vbias,开关内侧连到gate,加一个tie low nmos

搞不懂是不是我理解能力不行...

楼上正解,bias通路断掉,下拉到地

还是有图好理解,谢谢啦!