请问如何解决棒线电感引起的振荡

时间:10-02

整理:3721RD

点击:

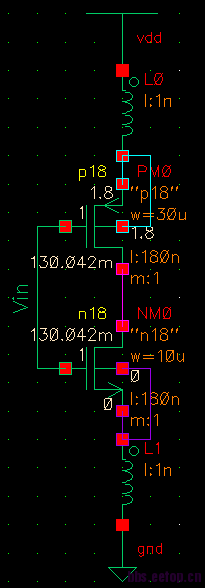

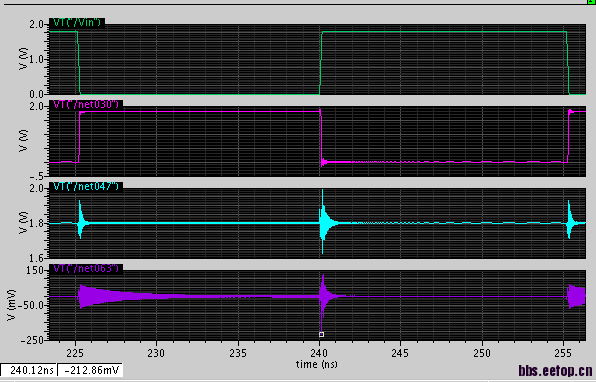

如下图所示,一个简单的反相器,在加上1nH电感模拟棒线后会引起振荡,振荡波形如下所示。

分析原因可能是方波上升沿和下降沿会在管子的源级产生尖脉冲(时钟馈通?),尖脉冲包含的频率非常广,棒线电感与管子的寄生电容将某一频率的信号滤出来,导致了振荡。

分析原因可能是方波上升沿和下降沿会在管子的源级产生尖脉冲(时钟馈通?),尖脉冲包含的频率非常广,棒线电感与管子的寄生电容将某一频率的信号滤出来,导致了振荡。现在我想问的就是如何能消弱或者避免这个振荡呢?

绑线不光有电感,还有电容电阻的

这个再正常不过了,没法避免,有本事就不要让电流流过电感

多加电 decoupling cap 会好一些

谢谢上面两位的回复,我也考虑到用理想电感代替棒线可能会引入误差,但我加入串联电阻、到地电容后发现依然有振荡的现象,可能是尖脉冲包含的频率太广,以至于无论采取什么方式的滤波都难阻止振荡。

这个震荡频率很高啊,不会进入芯片内部的。你电源地间没有电容吗?

看来从来没设计过电路啊,连基本的power management的概念都没有啊

振荡频率的确很高,或许经过pad后就会衰减掉了,但是现在仿真会很影响仿真速度。

整体电路当然要比这复杂的多,这只是对问题的一个简单描述而已。如果不加电感仿真结果很好,加上电感后就会出现类似的问题。

片上电容不可能做到很大,对这个问题没什么优化;我现在仿真用的是理想电压源,加片外去耦电容是没意义的。

我想要解决这个问题的主要原因是,它会拖慢仿真速度,大家都知道的:频率越高,仿tran的步长就越小。所以还请各位高手帮忙。

这种东西很正常 , 虽然有纹波但是不会影响到你inv的判决 就不需要考虑

power ground bounce ? ..

降低 rise/fall time ..

實際 CHIPlayout 有 impedance 會更慘.

還有電感和PACKAGE有關

soicsop8dip8dip16 全都不同

DIE太小PACKAGE 太大死更慘

改 down bond ..