求助环形振荡器仿真问题

时间:10-02

整理:3721RD

点击:

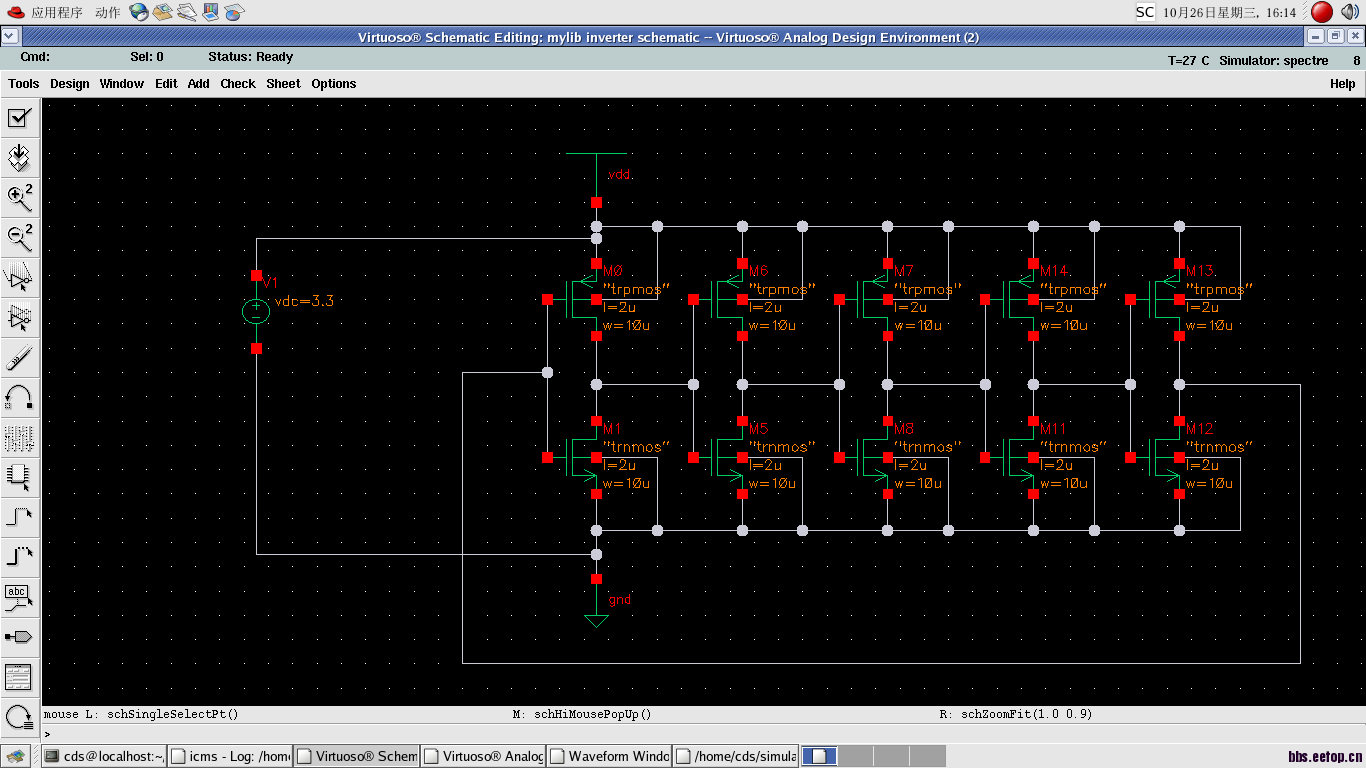

我设计了一个环形振荡器,但是仿真出来的频率和计算相差挺大的,这是什么问题呢?

Vdd=3.3V,pmos 和nmos的w/l=10u/2u,计算出来的结果是频率为179.7MHz,但是仿真出来的频率为367MHz,相差将近一半了。

是软件设置的问题还是什么问题呢?

还有,Vdd是根据什么设定的呢?

谢谢各位高手啦~

如果我将Vdd改为1.8,频率就差不多了,难道这个vdd可以随便改?

菜鸟问题,有木有好心人帮帮忙呀,急

Vdd=3.3V,pmos 和nmos的w/l=10u/2u,计算出来的结果是频率为179.7MHz?怎么计算的?

频率肯定电源电压有关啊,反相器的延迟就是负载电容的充放电,所以td=CL(Voh-Vol)/I,Voh就是Vdd,I为偏置电流,具体的频率就只能你自己算啦, 还有你用的工艺也不知道啊

是用这个书上的公式算的,呵呵。

偏置电流怎么算,可以仿真出来吗?之前我没有用工艺库,用的是自带的analoglib,我还有一个.18的库,我试试看。

其实说白了,我是想知道这个设计的振荡器是如何能验证的,最终能证明这个振荡器是对的。

你这个振荡器的输出电压都基本上在OV以上,不是正负交替 这个可以吗?

Read the PLL chapter of Razavi's textbook first

应该不是这个问题吧

怎么起振的

估计和你使用的工艺文件有关,你可以看下你用的那个.18工艺库的文件的sheet,看下说明是不是3.3v的。