我觉得运算放大器的偏置电路很难

时间:10-02

整理:3721RD

点击:

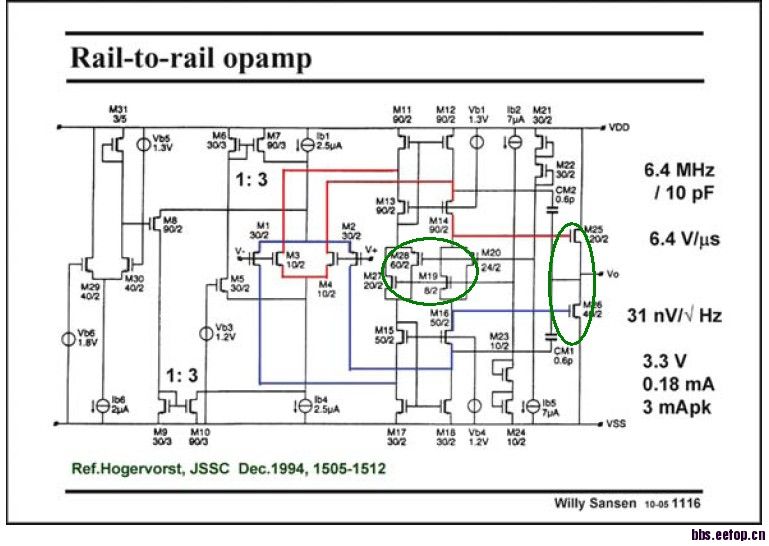

各位前辈同学大家新年快乐!最近我在学习设计运算放大器,感觉运算放大器的结构还是易懂,但是感觉偏置的电路的设置比较难,而且一般的书又没有详细讲,不知道各位前辈以前是怎么学习的,下面附上一张图,是我最近想模仿的rail-to-rail运放的图,图中画上绿色圈圈的是我不太明白应该怎么设计宽长比的地方。而且输出级的rail-to-rail应该满足什么样的条件才能输出VSS-VDD?好像并不是用了AB类输出级就一定能输出VSS-VDD,好像还要满足一定的条件,但是我不知道,所以想请教下各位前辈同学。

我知道这个是project,哈哈........

你好!你猜的也没错!也差不多算是project,不过是练手性质的。运放是我做的DAC中的一块。欢迎提供建议!

帮忙顶

这个要看是用什么工艺设计,不同的工艺设计时mos的迁移率会有所不同,因此,宽长比也会有所不同!

前面两个圈是浮动电流源吧,第一个起到了电流源负载的作用,由于使用了宽摆幅电流镜,去掉M27和M28那负载阻抗只有1/gm了;第二个是对输出两个MOS管的栅极嵌位吧,类似于两个二极管的那种,这个理解的不是很清楚;M25,M20和M21,M22组成了跨导环,用来偏置输出级,为了方便可以取M20和M22匹配,M21和M25匹配,这样M25和M21的电流比就取决于两者尺寸比了。个人理解,嘿嘿。

下面那片论文上有讲解啊,可以看一下

帮忙顶

谢谢!浮动电流源我现在大概有个理解:如果把它换成电阻的话就类似把电阻两端电压由原来VB变成+VB和-VB。不晓得对不对,跨导环这个还不是很理解,需要查些资料!