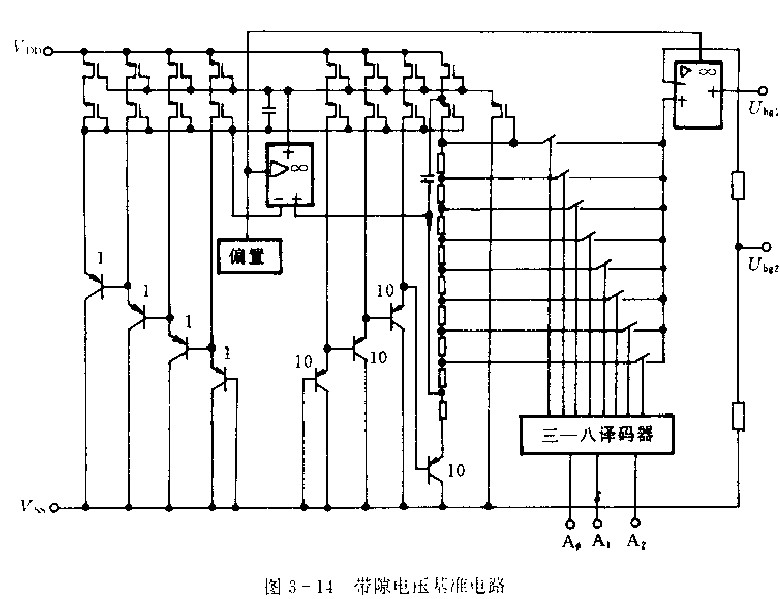

带隙电压基准电路问题请教!

一个bandgap 和3bitDAC

原理与flash ADC恰好反过来

方框是opamp

不用找原文了

好複雜

不懂

有牛人可以幫忙說明?

原理是不复杂,2楼说的对

不过很关心它的用处。

做什么需要这么多基准呢?

而其是不是有些年代的东西了,VDD应该比较高吧

整个电路是个LDO

译码器是对输出精度进行校正

,再赚点zh小钱

再赚点zh小钱

再赚点zh小钱

原理是不复杂

programmable volt reference

可以看看!

再赚点zh小钱

一直想要找中文的說明不知到可不可以找到

似乎输出电压也比较高。

这里的基准电压会要求有比较高的精度吧

看不出是LDO....反而覺得是programmable bandgap

这个基准也太难得一见了。

这是有个BGR电路,4个Ae=10和4个Ae=1和最右面Ae=10上那个电阻构成IPTAT产生电路,第一个运放是保证这个电阻上的电压与最左边Ae=1的发射极电压相等,第二个运放是缓冲输出,3-8译码器是用来修调输出电压,以获得最小的ppm,串4个BE结的没的是减小第一个运放失调对输出参考电压的影响。

good question!

什么地方要用到这么多基准源啊

Base of some of the BJTs are not connected to ground.

(Then they are not parasitic "substrate" PNP.)

In modern CMOS process technology you do not have this degree of freedom in your design.

路过看看