救命!PVT模拟到快疯了

毕业专题是一个capacitor-lessLDO regulator,一个简单的模拟电路.但是从8/21开始至今12/17日还在Pre-SIM,主要是因为PVT cornor的问题。牺牲了一切娱乐,而且也退掉补习,也没准备升研究所考试,就只是卡在这PVT角落上,快疯掉了!

我只是想把东西做好,牺牲研究所考试没关系,但要知道原因

模拟IC里面一位有名的研究学者,R. JACOBBAKER在他的网站上说了一些PVT的迷思。他举了一个例子,

Don’t let SPICE trick you into thinking that bytweaking the length and the

不要让spice骗了你,让你试着由调整晶体管的长度和

width of the devices you can make the currentsequal (yikes! ;-) and keep both

宽度,所以你可以使这两个电流相等,且保持让两者

devices in saturation (always)

都在饱和区,因为这个和PVT有关

专题里面的电路都是要偏压在饱和区。学长要求全部PVT(TT SS FF SF FS,+ -10%VDD,-40~120度)都要饱和。光调MOS长度和宽度就调了三个月。好不容易在模拟上"看起来"全角落都饱和。

LDO规格中有一个LOADRegulation要求要<50ppm/mA

我的规格在TT 25 VDD可达到20ppm/mA但在某些角落下高达1000ppm/mA

因为规格表上要附上的是最差数据当作保守数据,但明显的1000ppm/mA这个模拟PVT的结果会让我这一辈子毕不了业

网络上也有人问过为什么LDO的PAPER只有打上一般状态的数据而不是最差数据(答案有两种:一个是过不了,另外一个是不同设计考虑有不同PVT,这我可以理解)请问

1.但我到底该怎么办?是要附上20ppm/mA的数据呢?还是真的要打上最差保守数据(1000ppm/mA)

2.又要用什么样的态度去看待PVT的模拟呢?为什么几乎全部的LDO的paper都只有附上一般状态下的规格?

仔细检查过后知道是因为Voff_set造成的。但会造持成Voff_set就是因为PVT的不理想,(让电晶体管看起来"饱和"可以经由调整,但Voff_set在模拟中是无法控制的。)

问题:同学为了考研究所,故意放掉某些过不了的corner,只放TT 25的数据。

哎,问题都描述不清楚,

已经重新排版过后了!如有不详尽的地方请通知

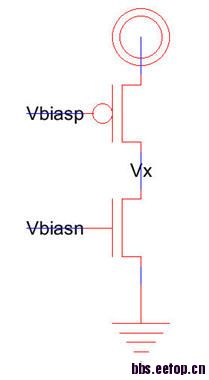

确实很多论文里放最好数据,但如果报告里要求worst case就一定要worst case,analog ic不是任何时候都追求某一参数的最优化,而是要明白原因以及改进要付出的代价。比如你说性能差是因为offset,那就想方法减小offset.btw,你的cascode偏置电路怎么杨的,好的电路需要在corner下有某种tracking.公司里肯定是worst case,typical没意义。当然好的design,worst和typical不会有太大差别。

运放基础不牢就开始做LDO。

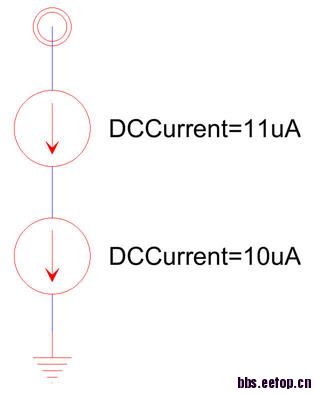

千万不要想着调size去让MOST饱和,1.先确定每个MOST要多少的Vod=Vgs-Vth (od, over drive),从而给其Gate端加合适的Vbias,2.确定MOST的SIZE,让其处于饱和区,也就是Vdsat>Vod,通常要留50mV以上的margin才可能在所有PVT下都饱和,也就是Vdsat-Vod>50mV。最后一点,不知道你第一张图什么意思,不可以用ideal Voltage source做bias voltage,用ideal current source * diode产生bias voltage,也就是current mirror.

load regulation太大,说明你的output impedance太大,也就是loop gain不够,初步看起来,应该就是你的OPAMP都已经逃离饱和区了,导致loop gain不够。饱和问题解决后这个问题自然会跟着解决。

增加DC loop gain有助于提高load regulation

这电路做的离毕业还早着呢. 对性能指标的理解好像还不透彻.电路搭好像也没有考虑很多因素. 哎, 找两篇论文过来抄写50遍再说.

本科论文已经做的不错了

其实有时候过于在意所有的corner,去找worst case会有一点钻牛角尖,很有可能所谓的worst case只有万分之一出现的可能

也许你的monte carlo simulation results,可以在3 sigma以内

但是分析下worst case影响性能的因素是必要的

trade-off

这个电路没有补偿,不会稳定吧?!