向各位大侠求助,几个关于LC CMOS差分VCO噪声的几个问题

时间:10-02

整理:3721RD

点击:

我的LC CMOS差分VCO噪声在10K的时候差不多一直是-39dB,我调节电路中MOS管的W/L过后(调节幅度比较大)为什么相位噪声一点都没发生改变呢?out noise也一点都没发生改变!请问能分析一下大致的原因吗?

坐等各位高手解答啊!

坐等各位高手解答啊!

你看下noise summary的噪声贡献,哪个是最大的,你那个总的噪声有可能主要是尾电流偏置的噪声

为什么要看10k点的相噪?难道你的PLL带宽10k都不到?

我的VCO带宽大概是1G的样子,这个和看10K的相位噪声有什么关系呢?为什么不看10K的相位噪声呢?

踩踩,嘿嘿

果然是尾电流的原因,谢谢这位大侠了啊! 现在我的尾电流为430uA不知道会不会太小了?

直观感觉数值上是有点小,不过也不一定,要看你的其他限制条件了.....

1.1G是谐振频率,不是带宽

2.VCO的相噪最终是要算到PLL里的,PLL环路对VCO是高通的,所以VCO相噪小于PLL带宽的部分基本都会被滤掉,差一点也没关系,关键是带外的相噪要好。

现在做的这个VCO是3.6GHz到4.6GHz的,所以说带宽是1GHz没有错吧!

PLL里面是有一个低通滤波器,我前面指的10K 100K 1MB的意思是偏离VCO当时频率10 K 100K 1MB时候的相位噪声

1.这是调谐范围,tuning range,不是带宽

2.你还是没有明白VCO的相噪是怎样影响PLL的相噪的,频偏和LPF的带宽是对应的。

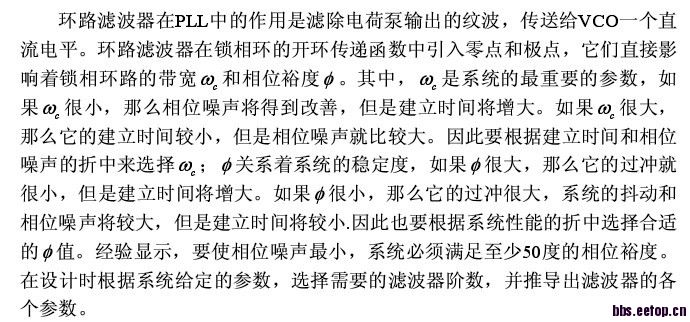

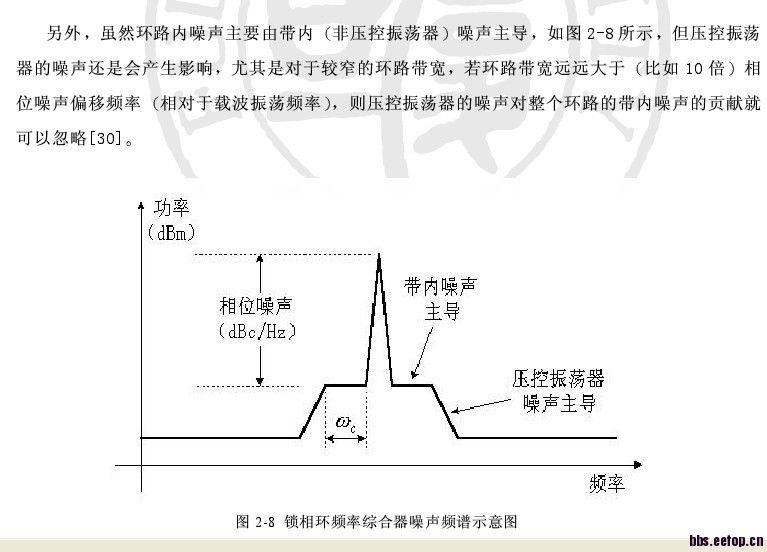

额、、、做确实没怎么去研究过PLL,刚刚研究了下PLL的低通滤波器,如下面图片所说,还是不太明白你的意思、、、、能说详细一点吗

PLL环路对于LPF之前部分(PFD,CP)的噪声是低通的,之后的部分(VCO,divIDER)是高通的。

或者你可以简单地理解(当然不太准确)为:VCO的噪声中只有频偏高于带宽的那部分才是真正的噪声,因为低于的那部分会被LPF滤掉。

明白了 谢谢了!

不错不错