VerilogA仿真求助

时间:10-02

整理:3721RD

点击:

用verilogA写了一个简单的Model,然后将其生成的symbol调用至一晶体管级的原理图中,结果仿真速度奇慢!

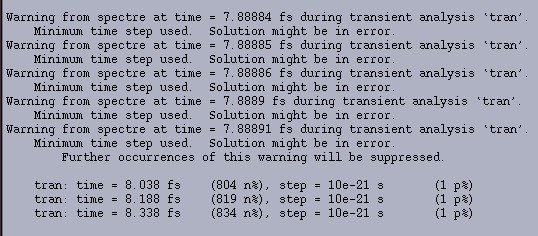

出现warnning,请问有人碰到过没?有什么方法解决吗?谢谢回复

出现warnning,请问有人碰到过没?有什么方法解决吗?谢谢回复

公开你的设计及仿真细节,否则没人帮得了你

现在问题大概是这样的:

我用以noise_src+vdc作为一简单倒相器的VDD,打算以此来分析VDD噪声对该倒相器的抖动影响;

但是仿真时间很长,步进如一楼图中所示。

我想知道这种方法模拟电源噪声时,如果想通过瞬态来分析是否可行;否则有什么其它方法,谢谢

这是很正常的情况,因为它仿真内部计算复杂时就出现这个,这个不影响最终结果

要学这个了来了解下

请问小编,veriloga是用什么仿真器仿的?

学习一下

应该是仿真器无法确定仿真时要使用的step大小,所以用了minimum step,导致仿真很慢;

解决方法可以试试在veriloga中加一条

- $bound_step(expression);

学习了