请教---诚请指点如何偏置套筒式OTA(有图)

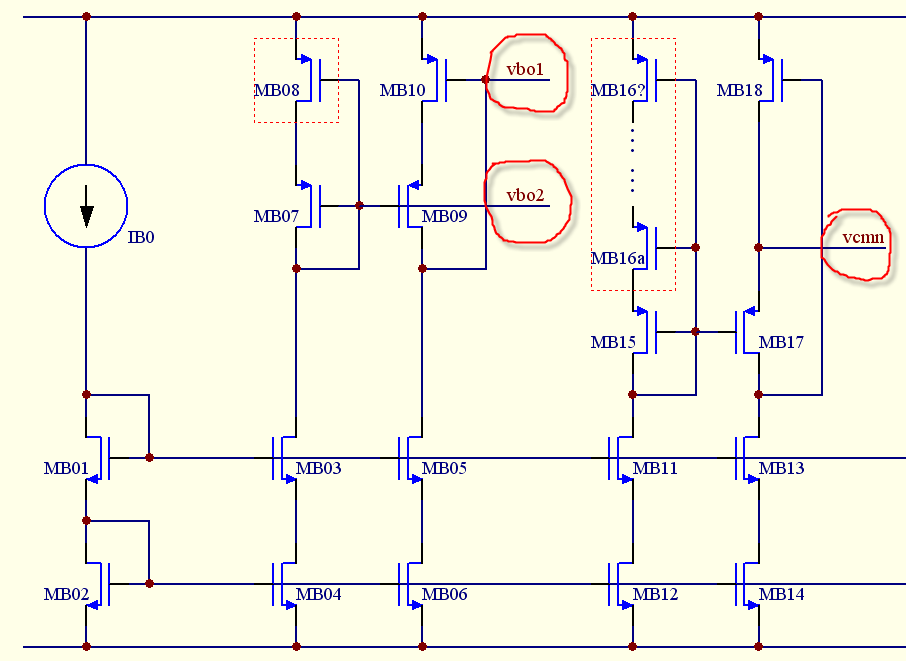

I could not run simulation, so here are my rough opinions: vbo1 and vbo2 might be OK, this is a high swing current mirror, MB08 and MB07 could be combined as one transitor or keep them intact. Their sizes can be calculated based on some references, such as Johns/Martin's book. But still, the current accuracy could be an issue due to the big Vds difference of MCO2 and MB09 and etc.As for vcmm, I have some concerns. How can you guarantee MC07/8 are in saturation region? You'd better leverage half amplifier cell to design the bias for these two transistors.

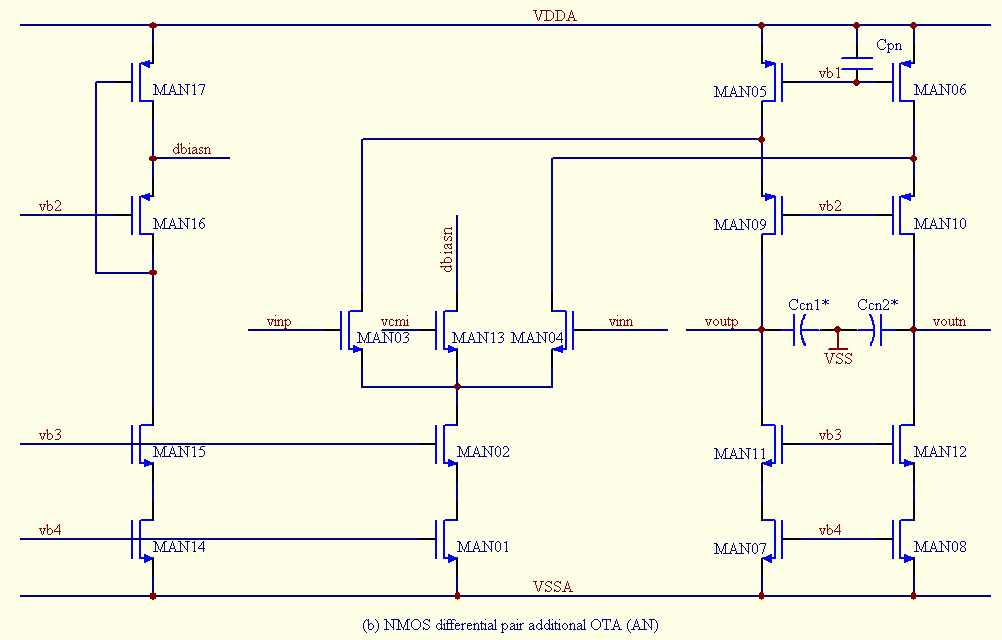

Sorry, I need to take a look at your AN as well.

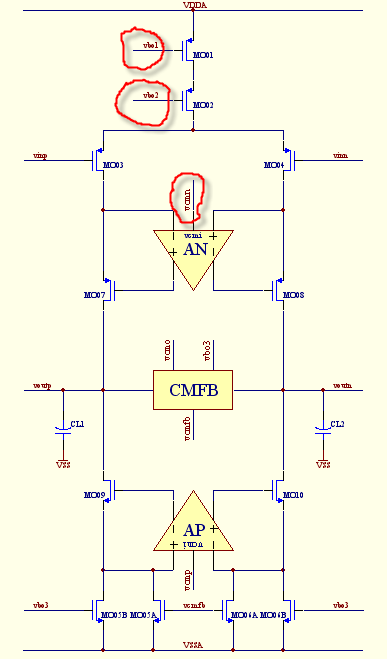

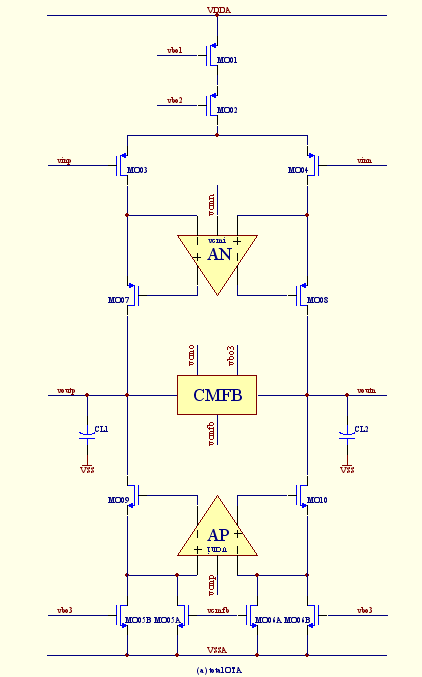

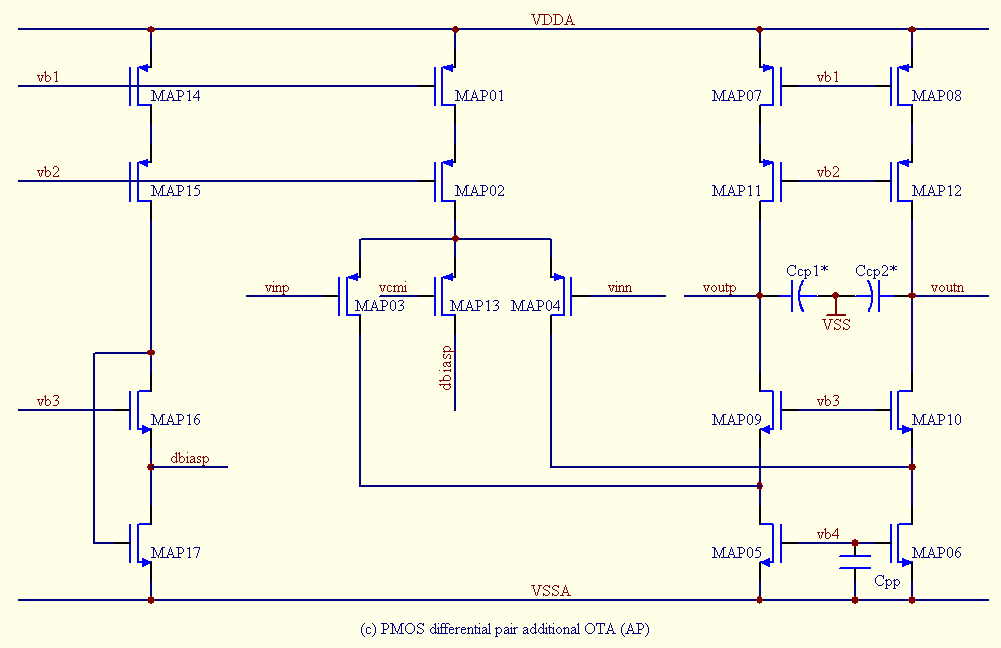

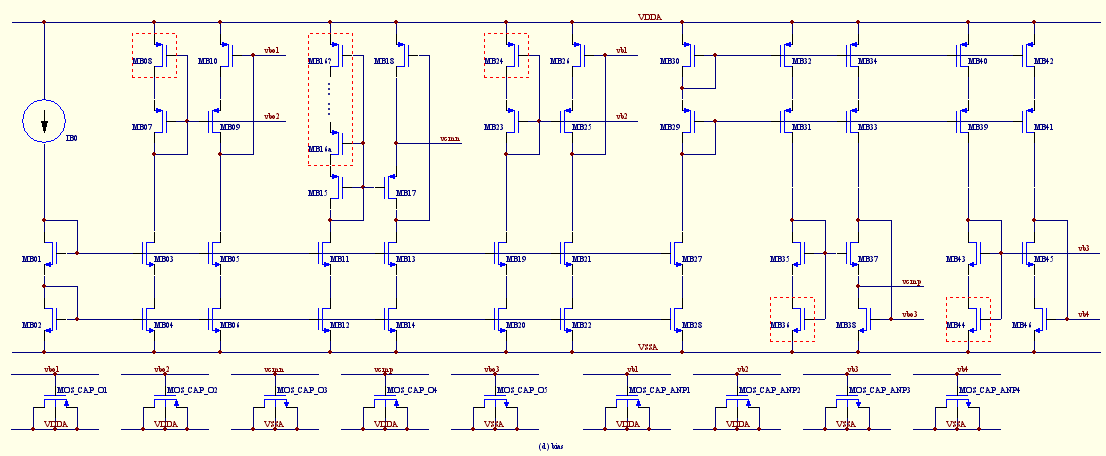

非常感谢ulsi123大哥的热心指点,关于MC07,MC08的饱和性问题,小弟的思考是:在整个运放输出摆幅足够低的条件下(电源=3.3V,输出摆幅=2.1V)有希望使他们处于饱和区。为了方便大家指点说明,现在重新把整个运放完整的原理图呈现如下,小弟非常担心偏置部分是否可靠,项目严重滞后,诚请大家指点指点。谢谢!(点击图片可以弹出更清晰的图形)

你那第3个红圈里的是偏置啊?,我还以为是共模电平呢

偏置电路肯定是可以工作的,至于可靠性其实也不会有你想像的那么可怕,只有你能保证在你关注的case下simulation 都通过的话,问题就不会很大。op 管子的工作状态应该完全是你设计的,并且留有一定的余量。

值得商榷的是你上边的偏置未必就是最好的情况,像这种辅助op bias的 design,应该尽量保持bias 的形式与你主op的对应控制点的结构一致比较好。在你这里,当op正常工作时后,两个输入管子会在共模电平附近,那么在你的bias 上mb17用 输入共模偏置可能会比较好。

另外你的辅助op输入共模控制的drain端是接到dbiasp(n)上,相当于接到一个diod管上,为什么不直接 tie to vdd or vss?一般的做法多是这样。我觉得辅助放大器直接用一个前馈的输入共模控制电压不太好,应该用共模反馈好一点

回6楼的

应该尽量保持bias 的形式与你主op的对应控制点的结构一致比较好

这是什么意思呢?

还有这种开关电容的cmfb应该怎么做ac仿真呢?其实MC07,MC08的是否saturate以及如何bias,是应该按照你的output common mode voltage要求来决定的

比如output common mode=1.2V, singal end Vpp=1V, 那么MC07 Vg>1.2+0.5-Vth07,基本上约为1.2V以上啦,当然需要考虑留一些margin

那么就可以从电源往下接两个或三个diode connect PMOS,从底层PMOS 的source端抽出vcmn

在这种结构中,想做current mirror bias比较困难,还取决于input common mode voltage

BTW,这种结构的opamp output range很小,而且应用在S/H里,input common mode 无法与 output common mode相同,有时会相差挺大的,这也会有一定的risk这个帖子不错。过段时间我会写一个有关套筒式的设计流程,到时候上传共享一下

为了方便大家进一步指点与讨论,现在对大家的疑问或建议尽本人的努力作如下说明,希望大家批评指正,欢迎大家发表各自的观点,相互包容,共同进步。谢谢!

0。说明0

为了说明方便与保持术语传承的连续性,参照文献【1】中的命名方式,规定如下:

总运放:total ota

原始运放:original ota---"O"

nmos输入差分对辅助运放:additional ota with nmos differential pair---"AN"

pmos输入差分对辅助运放:additional ota with pmos differential pair---"AP"

例示:MO07中的"O"表示该MOSFET属于原始运放的一个组成部分,其余的以此类推。

1。说明1

5#论点:“你那第3个红圈里的是偏置啊?,我还以为是共模电平呢”

小弟理解:对这种gain-boosted OTA, 小弟的理解是:电路正常工作后AN与MO07、MO08形成局部的闭环反馈回路,结果使VD_O03与VD_O04的共模电平=vcmn,即这个偏置电平通过局部反馈作用控制了MO03、与MO04管的漏端的共模电平。以此同时,当MO07、MO08工作于饱和区的情况下,通过一定的电平平移,这个偏置电压也间接控制了MO07、MO08的栅极共模电平。

2。说明2

6#论点:“值得商榷的是你上边的偏置未必就是最好的情况,像这种辅助op bias的 design,应该尽量保持bias 的形式与你主op的对应控制点的结构一致比较好。在你这里,当op正常工作时后,两个输入管子会在共模电平附近,那么在你的bias 上mb17用 输入共模偏置可能会比较好。

另外你的辅助op输入共模控制的drain端是接到dbiasp(n)上,相当于接到一个diod管上,为什么不直接 tie to vdd or vss?一般的做法多是这样。”

小弟理解:(1)的确,大哥说的很对,很多论文里都是采用主运放与辅助运放共用同样的偏置,并且很多的主运放和辅助运放都是折叠共源共栅的结构,可是他们很多人的考虑出发点是简化电路设计,而且主辅运放结构的一致性也为这种作法创造了有利条件。然而小弟的考虑出发点是尽可能提高辅助运放的第一个非主极点的频率,根据文献【2】提到的设计方法,要求辅助运放的第一个非主极点约等于10倍的GBW,基于这种考虑,小弟希望把vb1、vb2适当调低,把vb3、vb4适当调高,这样就可以把相关的MOSFET尺寸缩小,进而减小寄生电容,最终提高辅助运放的第一个非主极点频率。

(2)根据“说明1”中的理解,假设输入差分电压为零,当电路正常工作后MO03漏端电平为vcmn,如果用输入共模电平来偏置MB17,则必然造成MO03漏端的电平比栅极的电平高出一个阈值还要多,这可能导致MO03退出饱和区。(3)的确,大哥说的很对,很多论文都是直接把MAN13(MAP13)的漏端接到VDDA(VSSA),小弟是希望MAN03、MAN04和MAN13之间的VDS更加匹配,从而使MO03与MO04的漏端共模电压更精确的跟随vcmn。

3。说明3

7#论点:“我觉得辅助放大器直接用一个前馈的输入共模控制电压不太好,应该用共模反馈好一点”

小弟理解:两种结构都有看到,小弟还不太明白这两种共模反馈各自的优缺点,还希望大哥多多指教。

4。说明4

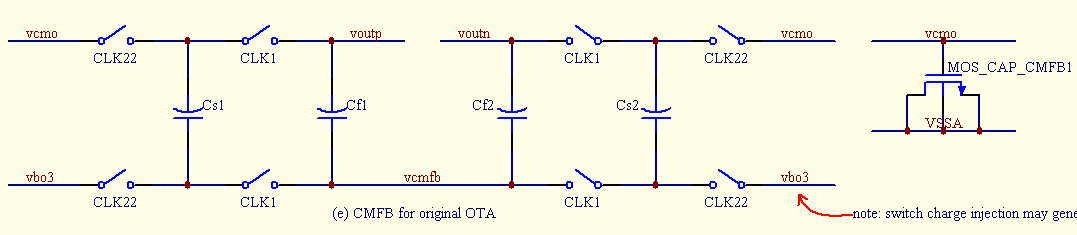

8#论点:“还有这种开关电容的cmfb应该怎么做ac仿真呢?”

小弟理解:以前作个用HSPICE来仿的,细节忘记了,给一个思路吧,方向对了就好弄了,具体作法是:先跑一小段时间的瞬态仿真,然后再.AC

5。说明5

9#论点:“其实MC07,MC08的是否saturate以及如何bias,是应该按照你的output common mode voltage要求来决定的

比如output common mode=1.2V, singal end Vpp=1V, 那么MC07 Vg>1.2+0.5-Vth07,基本上约为1.2V以上啦,当然需要考虑留一些margin

那么就可以从电源往下接两个或三个diode connect PMOS,从底层PMOS 的source端抽出vcmn

在这种结构中,想做current mirror bias比较困难,还取决于input common mode voltage

BTW,这种结构的opamp output range很小,而且应用在S/H里,input common mode 无法与 output common mode相同,有时会相差挺大的,这也会有一定的risk”

小弟理解:很赞同大哥的观点,小弟预设的共模电压是比VDD/2偏低的,VDDA(3.3V)-6个饱和电压后,保证输出幅度约2.1V的情况下确定输出共模电压,大概是vcmo=1.45V;确实这种结构输出摆幅很小,但节约功耗非常可观,由于小弟的系统刚好可以是使该放大器输出幅度小于2.1V,所有当时就选这种套筒式结构。关于输入、输出共模电压的问题,小弟希望通过开关电容网络来补偿,理论上已经推导完毕。

以上仅仅是小弟的一些愚见,由于经验不足考虑不周,有些地方难有一厢情愿之嫌,真诚大家批评指正,小弟认为,把gain-boosted OTA 弄好了对作基带模拟的将有极大好处。希望大家一起努力,共同讨论,多多指点,谢谢了!

参考文献

【1】klaas bult and govert j. g. m. geelen “a fast-settling cmos op amp for sc circuits with 90-dB dc gain”

【2】mohammad mahdi ahmadi “a new modeling and optimization of gain-boosted cascode amplifier for high-speed and low-voltage applications”学习啊。

学习了

saiaoying

[quote][/quote]小弟理解:对这种gain-boosted OTA, 小弟的理解是:电路正常工作后AN与MO07、MO08形成局部的闭环反馈回路,结果使VD_O03与VD_O04的共模电平=vcmn,即这个偏置电平通过局部反馈作用控制了MO03、与MO04管的漏端的共模电平。以此同时,当MO07、MO08工作于饱和区的情况下,通过一定的电平平移,这个偏置电压也间接控制了MO07、MO08的栅极共模电平。

小弟理解:(1)的确,大哥说的很对,很多论文里都是采用主运放与辅助运放共用同样的偏置,并且很多的主运放和辅助运放都是折叠共源共栅的结构,可是他们很多人的考虑出发点是简化电路设计,而且主辅运放结构的一致性也为这种作法创造了有利条件。然而小弟的考虑出发点是尽可能提高辅助运放的第一个非主极点的频率,根据文献【2】提到的设计方法,要求辅助运放的第一个非主极点约等于10倍的GBW,基于这种考虑,小弟希望把vb1、vb2适当调低,把vb3、vb4适当调高,这样就可以把相关的MOSFET尺寸缩小,进而减小寄生电容,最终提高辅助运放的第一个非主极点频率。

(2)根据“说明1”中的理解,假设输入差分电压为零,当电路正常工作后MO03漏端电平为vcmn,如果用输入共模电平来偏置MB17,则必然造成MO03漏端的电平比栅极的电平高出一个阈值还要多,这可能导致MO03退出饱和区。(3)的确,大哥说的很对,很多论文都是直接把MAN13(MAP13)的漏端接到VDDA(VSSA),小弟是希望MAN03、MAN04和MAN13之间的VDS更加匹配,从而使MO03与MO04的漏端共模电压更精确的跟随vcmn。

这两点你说的很对,是这样的。赞同。

其余对于CMFB的具体仿真我也不是很清楚,希望有牛人能讲解下see see

关注楼上的 大侠

不知lz仿真AN/AP分别与MC07、08/09、10时是否会遇到次极点与第三极点太近的问题

关注中。

受教了,,