sigma-delta ADC 调制器问题

时间:10-02

整理:3721RD

点击:

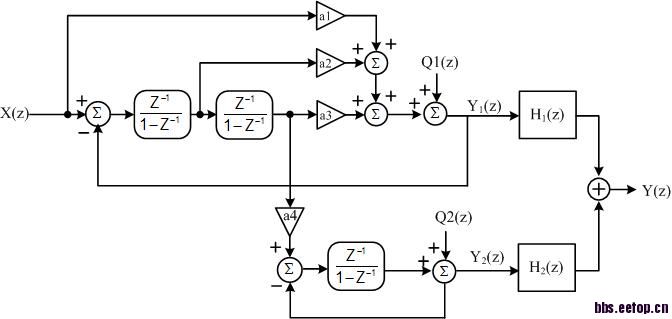

最近在做sigma-delta ADC,调制器架构如下图所示。采用的是三阶(2-1)MASh结构,第一级2bit量化,第二级1bit量化。

对该架构进行了simulink验证,调制器输出功率谱如下:

调制器实际电路仿真下,其功率谱密度如下:

比较两个功率谱密度,很容易发现:电路仿真下,带内的噪声几乎的平的,没有被压下去,导致信号与带内噪声的差只有80dB左右。远远小于simulink中的130dB。

现在的问题是,为什么在电路仿真中,带内的噪声没有被压下去?是做fft时没有加窗函数原因还是调制的电路设计有问题?

急求高手解答....

用hann window FFT

你的理论设计是多少位的啊,你的第一级采样电容大小?热噪声理论上是多少啊

直接fft和加hanning 之后fft,对调制器输出而言,哪个更能反映实际频谱

输出24bit, 采样电容1p左右,热噪声1.1*10-8V左右

采样电容太小了吧,osr=128的时候,你要达到-110db的带内噪声,需要4p以上的电容啊,你这个24bit的,带内噪声要小于-146db,加上-20db的余量,采样电容应该大的惊人啊

如果真按24bit 146dB来计算,采样电容会相当大,但是事实上SNR不可能达到140+ dB,所以估算的时候是按照16bit的有效位来计算的,然后加上了一定的余量

我以前做了个16bit指标的,采样电容用了3pf,osr=128的,测出来结果是14bit,你可以参考一下

加窗和不加窗没啥区别。

如果你有足够耐心,慢慢移动fft 的起始点,不加窗也有可能得到很好的fft 图

好的,谢谢哈。问题的原因我已经查出来了,主要是因为调制器输出中含有几mV的直流失调,所以导致做fft分析时加窗与不加窗会有区别,不知道你当时做的时候是怎么处理直流失调的

这种方法我也试过,确实取点的位置不一样,fft分析结果就不一样,但是如果每次分析都这样处理的话,就太麻烦了。而且hanning窗可以防止带外的噪声混跌进带内,所以现在看来调制器输出加hanning窗是绝对应该的

是要加窗函数的,我当时加的blackman窗,窗函数对直流信号的衰减还是不错的

最好采用调制器两路输出的差来做分析,这个直流成分会抑制的比较好,不要用一路输出减去共模电平来分析