bandgap求助

上个电路图看看,是不是运放调整范围有限啊。

可能是正负反馈出问题了

上电路图才能分析啊~

这话看的费劲啊,怎么输出电压一会vdd一会又1.2V到底是多少啊?

根据你的描述,我推测是你的启动电路将运放牵制了,意思是说你的启动电路的不能再运放启动之后就关闭工作,导致运放的输入电压牵制在0.7V左右!试一试采用PMOS输入管的折叠共源共栅运放,如果我推测的没有问题,换用PMOS输入管的运放之后应该可以工作,另外,你的启动电路需要修改,尽量保证电路正常工作之后,启动电路处于关闭状态!

有问题请回复,咱们继续交流!

楼上说得有道理,可能不是启动电路没启动,而是关不了,影响电路的支持工作了。

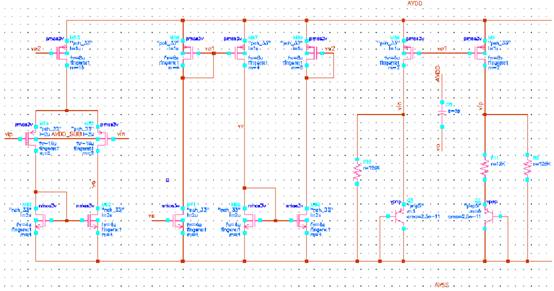

我是用的Pmos输入管啊,而且我看了下稳定后的启动电路的电流只有20n,说明已经关了啊,也就是我如果给VDD加DC激励,那么我的直流工作都很正常,启动电路此时无电流,但是如果给VDD加tran激励(0到2.8V电源电压),那么Vref就跟随上升到2.8v,说明根本就没启动得了啊,但是我换成对称式结构的运放,Vref就只上升到1.2V,也就是能启动,我觉得是结构的问题,估计是cascode管不好拉起来

你的电源激励是沿很陡的吧,你用什么仿真工具,你要看一下仿真过程用的是什么收敛

干说很费劲的

好了好了,我明天上图,大家一起讨论,肯定有收获的

还指望小编上电路图呢,怎么没有动静了?

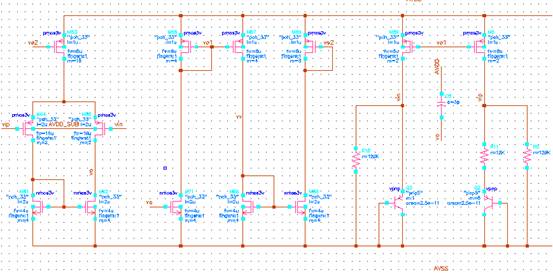

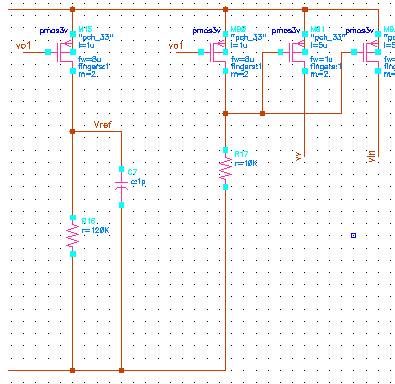

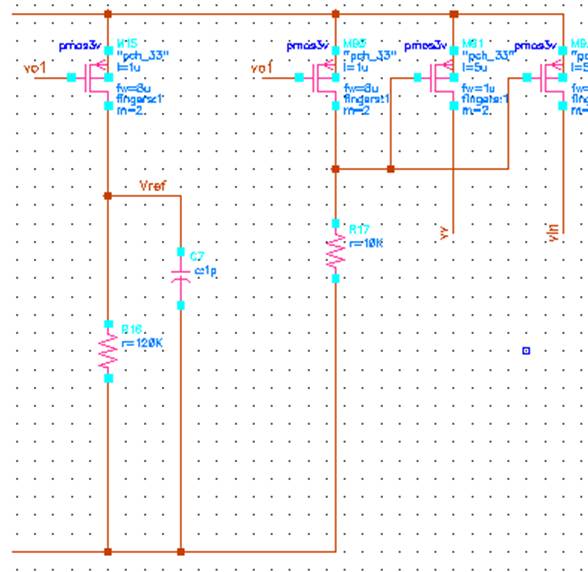

重新传下,刚才传的不

清楚

清楚

上电的激励与启动是有相关性的,在仿真的时候

不懂,能详细点吗

看下你折叠共源共栅运放的输入正负端有没有接反?

没有接反啊

没怎么看明白,但是感觉6楼分析的有道理

晕,这图画的,这么小的电路用那么多的net,截的也不清楚,结构看不清啊!

路过,看看。

你好,我想你的问题之所没一直没人解决是因为你的问题和图都太模糊了,说了那么久也没弄清楚你的问题是什么,我看了你的图好久,也没看懂你的电路图,何必弄那么多的结点,直接走线会很明了的。建议你先附上一张清楚的图,再清晰地表述你的问题。

cascode并不存在启动问题,但是非电流镜负载的全差分的cascode通常需要共模反馈,否刚会使得上管或者下管进入线性区。

Vref下面接的应该是电阻和PNP管的串联,而不仅是电阻,否则就不叫bandgap了。

你说Vref=VDD,那说你的你P管工作在深线性区,也就是说栅级电压(运放的输出电压)为0,说明你的运放没能工作在静态工作点上。