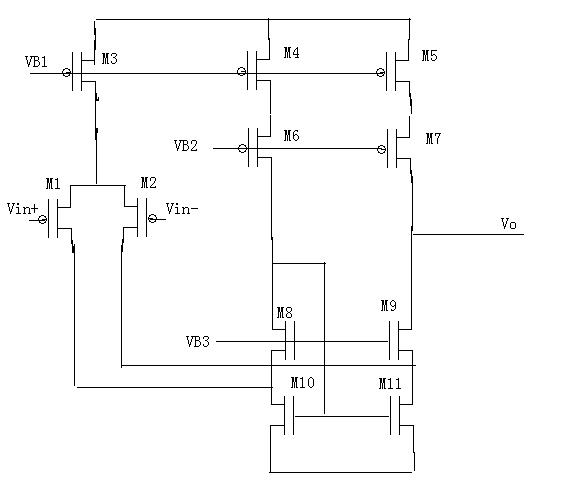

问一个floded cascode运放的问题

这个没啥好的,浪费一条支路的电流,增益少6dB。

我也遇到过类似的电路,是用来做比较器的...

楼上的,没浪费。增益还是gm1*Rout.

电流镜放上面下面都可以吧,我觉得没什么大区别。实在要说区别的话,就是平衡时vout输出电压不同。

用pmos电流镜,平衡时大概vout=vdd-vth;用nmos电流镜,大概vout=vth。

书上没讲的电路多了去了,自己按照书上的方法推一下就可以了。对应一下就行,不用真的推出书上那么完美的公式来。

应该不少6dB,你仔细算算?

cascode那个点是个低阻抗点,小信号电流大部分流入了这个节点。

既然不能流入上面的管子,那就一定流入了下面的那个管子。

cascode那两个管子可是构成反馈的噢。

小编去好好看看allen吧,讲的很清楚

好像和书上讲的区别不大吧

OK,可能是我错了,我还真没有仔细算。

还真有书上讲这个电路,sansen的analog design essential 英文版chapter7, page 226.

不知道有什么好处,实际中没见过这样用的。

8# goodsilicon

你肯定错了。

实际中就这样用的,如果输出电压比较低,这样用可以减少一点系统误差

我不知道

oh, my god!

实际中应该用的很多的吧

区别不大,非要说区别,这个电路可以省一支偏置电流产生电路

9# vdslafe zen

怎样减少系统误差呀?

thanks

最大的差别是PSRR:

理想情况下(1/gm<<Rds),对于NMOS mirror,从电源到输出VO的增益为0;

对于PMOS mirror,从电源到输出VO的增益为1.

输出的swing 会大点,输入的范围可以从很低的电压开始

这个电路用处还是挺大的

在做pipeline ADC 中gain-boosting电路一般会用,但是要该下结构

rail-to-rail 也会用输入的结构,不过是2个拼接

1. 节约了一路偏置

2. 折叠处的阻抗更低,高频极点更高

3. psrr+更好

4. 输出电压低时system offset更小

很常见的结构

真的比那种常见的结构还常见吗?

哪一种曝光率更高些?

jianjing526,你能解释一下为什么psrr+和offset更好么,说具体一点

to goodsilicon, 两种cascode的使用频率没有去对比过,对于一个特定的spec可能两者都可以用,用哪个纯粹是个人倾向

to smelly

psrr+之所以优于常规结构是电流镜的位置决定的,一般来说1/gm相对rds是个低阻通路;system offset=(Vout+-Vout-)/Aol, Vout+设定为op的输出,Vout-为对应的反向输出端(常规结构中为vcc-vgsp, 这个结构里为vgsn), 在Aol等同的情况下,Vout+小点system offset会好点

电流镜的位置跟psrr有关,在下面是抑制GND的噪声,在上面是抑制VDD的噪声。

没什么特别啊,看看书就知道了

swing較大, gain相同,

接p或接n當然有差

gmro*ro

gmn > gmp 接下rl較大

值得研究

可以增大输入共模范围

sansen的书上讲了

大信号是不一样的, 对电容充电的电流另外一种结构的一半。就是说 slew-rate,会有点问题。

主要用在输出平衡电压低的场合,两级运放的第二级可以直接用 nmos管,要不就只能用pmos,或者common-drain + nmos.

值得一想