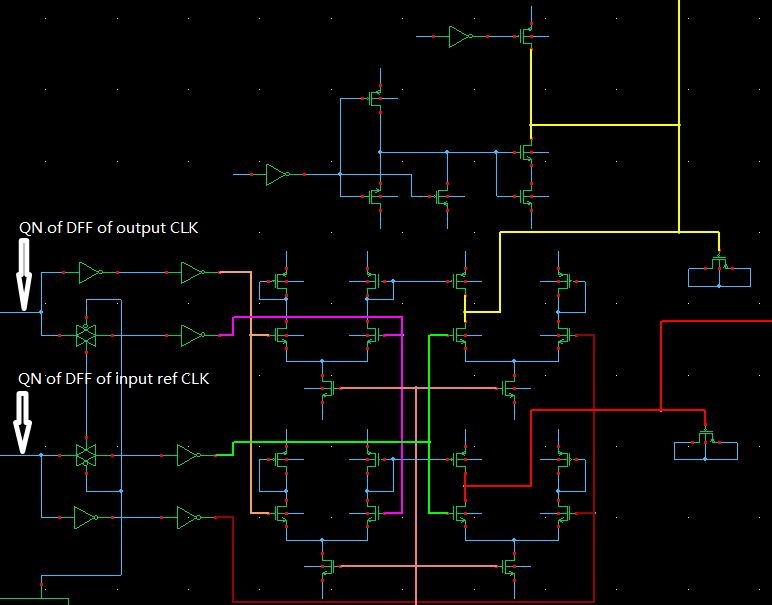

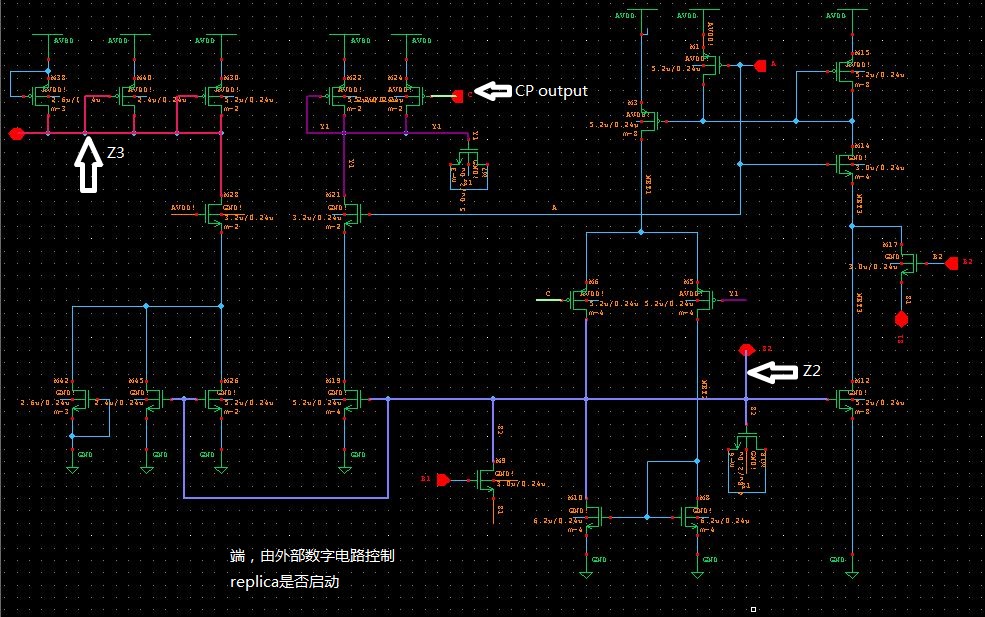

一个PLL的PFD&CP&LPFF电路,大家帮忙看看,我贴图

大家看图说话,我不明白那个LPF的零点时从哪里引入的,是从replica bias中吗?是怎么实现零点的?

最下面的图上,Z2,Z3是通往差分VCO去的

没人在嘛?

没人?

那位做PLL比较熟,给讲讲啊

没人知道吗?

hao!

5# deepblue1178还是没人?

图太乱,看不清楚

图太小,看不清楚!

厄。 大家哪里不清楚可以问

因为你说有运放 Y/N?

所以我设这个运放是Filter的主体用的Y/N?

在运放的 input/output 置Z1 Z2 Z3产生FIlter function Y/N?

还是你是用电流的倍率ex: IB*I 做合流产生zero?

一般而言,找问题可以先用手算->matlab->verilog-A->Hspice

一步一步来吧 否则你无法知道每个node该看到什麽怎可能找到问题呢

不过 我还是听不太懂您的问题点儿11# tulipbear97

谢谢你的提点,我的问题是为什么有两个CP环路? 通过仿真我发现,上面的CP环路会先工作,当PFD的输入端频率基本相同时,上面的CP输出电压就一定了。而第二个CP有可能是和相位相关的。很明显的,依您的仿真,当频率相同一个CP就不再动,也就是它是FLL loop 即是较PLL少了一个原点的pole

若以type-II Transfer function来看,就是少一个s 於pole(FLL path)

两相加会有 k1+k2/S=(k1*S+k2)/S

zero comes out ! It's beautiful, do u love it?LPF的零点就是充放电的大电容和与它串联的电阻共同产生的吧

另外一个并联的小电容是消除纹波用的,但会引入一个极点

小编计算一下LPF的阻抗即可Thanks!

这个应该是反向提出来的图,还是应该把电路好好整理整理,然后把电路的拓扑结构画出来

自己也看得清楚阿

电阻电容串联就形成一个零点同意tjjbraye 的说法,把电路整理一下再贴上来大家分析一下。

13# tulipbear97

相当感谢! 但是我还是不太懂您说的意思, 这两个CP是完全一致的,也就是说如果有相位差,就会有静电荷存在于电容上,不管是充放电。但是为什么这个环路的电容电压不变了呢?14# sdscj

电容电阻串联的确是可以产生LHZ,但是怎么等效呢?顶一个了。

two loop cp is for avoid charge sharing

the replica bias, you can find menatis paper" low jitter pll and dll...."

zero pole is add Res series with cap21# mmic1978

没有找到与CP串联的电阻。 我觉得还是前面有个达人说的对,通过FLL和PLL共同工作引入零点,但是这个机制还是不太明白 请问有相关的论文吗》21# mmic1978

在您推荐的论文中,我看到了需要的东西,但是有一点不太明白!

Vctrl=Vbp,这个是对的。后面又说 Vctrl defines the lower voltage swing limit of the buffer outputs. 这句话该怎么理解? VCO的设计中不是应该尽量保持摆幅恒定吗?最大摆幅应该是Iss*Rd,我的理解是Vbp和VBN应该差分变化来保持摆幅恒定。但是坐着的这句话是什么意思呢?paper 有误,Vsw 是由 VDD变化到Min(VOUT)

应该是 VDD-VCTRL=Vsw (PMOS 作为 RES Load)

你可以尝试仿真单个PMOS,gate bias with VCTRL and Vsw=VDD-VCRTL then DC sweep the VCTRL para...you will find the replica center symmetric I-V curve我又琢磨了一下,作者的意思应该和您说的意思一样。Vctrl定义了Min,VDD定义了Max。

现在我明白了,这个对称负载的含义:即两个gm并联。通过replica的负反馈,使得Vout=Vctrl(因为这两个点被接在运放的输入端了)

另外,我可以通过同时改变Vctrl和Id的大小来控制恒定的摆幅。但是问题又来了,如果同时改变Vctrl和ID,保持了摆幅恒定,但是就没法调节f0了,因为电阻被Vctrl和Id的相反变化抵消了。这又该怎么解释?

还有一个问题,用hspice-rf怎么仿真Kvco和 Kpfd? 见贴http://www.eetop.cn/bbs/thread-211869-1-1.html有人吗

自己顶一个

图中的schematic 太乱,就不能整理的清晰点 ?

看不清楚

gg 1# deepblue1178