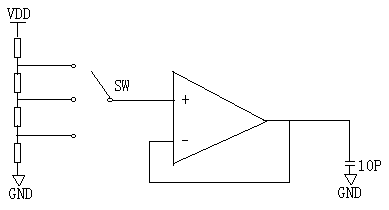

请教此运放的性能参数是否满足要求

增益100db左右,带宽3M,相位裕度82,摆率6v/us。

小弟初学,恳请各位大哥指点。

又沉下来了,自己顶上来,大家帮帮忙

能满足要求,不过还要看你对静态误差和动态误差的要求!

不知道你说的带宽是指什么,如果是主极点的频率,感觉实际做不了这么大,如果是GBW实际上又太小!

是单位增益带宽。因为输入级的电流源提供的电流很小,原电路里这个运放是P管输入,输入对管的W/L不大,而且PMOS尾电流源的W/L也不大,大概提供10u左右的电流,所以带宽只有3M左右,而且摆率也只有6u/V。因为考虑原始电路是这样管子参数设置,所以个人判断此运放的带宽和摆率应该不大,但是不知道自己的判断是否正确,还有不确定怎样的值算是合适。

SR看样是能满足要求,带宽是3M,那它的setting time 是多少 不知小编考虑过没

好像有点不够哦

可以实际仿一下,希望能小编继续跟帖

一般来说 GBW比开关频率大2-3倍

因此如果你的开关频率是1M左右的话

这个运放应该是符合要求的。

因为这个运放是用在采样保持电路里的(和前面画的电路图有点矛盾,不好意思,呵呵),它的反向输入端接的是开关电容,周期为4u的时钟,其中有1.8u左右是用来采样输入信号,2u左右保持。输入信号的摆幅最大只有2.4V。现在实际仿真得到,SR=5.3V/u。仿真时输入信号如果变化2.4V,输出采样信号可在1u左右时间里稳定(小于1.8u的采样时间)。这样看起来可以满足要求,但是不知道这样仿真是否是可行的,或者足够的。

大家帮忙,谢谢。

大家不要光说行还是不行。最好把考虑的原则或公式写出来。方便大家触类旁通。

这个似乎跟你的建立精度有关系的,如果是10bit的建立精度那么建立时间大概为7*(1/3M)=2.1u

谢谢楼上的,但是我这里不是用在AD/DA转换里的,只是在采样时间里将信号采样完成就行,保持数据正确,采样时间就是1.8u左右。

其实不能只看SR的,小信号的稳定时间通常比这个大的多,一般7个时间常数的时间能将输出的误差稳定在0.1%左右。

这就要看你对数值的精度要求,如果比这个要求低,所需要的稳定时间就少。

所以GBW也是很重要的。

谢谢楼上的大哥。冒昧问一下,“7个时间常数的时间”这里的时间常数是指什么,是1.8u的采样时间吗?

不是的,是指反馈后-3dB带宽所对应的时间,带宽越大,时间越小,稳定得更快。

很好的一个话题,顶

slew rate 肯定够了,原因明显不用多说

带宽够不够要看你要settling到多高的精度0.1%还是更高?根据指数公式(1-exp(-t/tao))得到时间

才可以知道够不够,你现在连精度都没有,还谈什么够不够呢

另外输入信号的SETTLING也不要忘了考虑,虽然输入管SIZE所谓很小,但是模拟的东西不是大概其,

是要讲精确定量的,如果电阻串阻值太大,OP再怎么好也满足不了最后要求