spectreVerilog仿真不正常,求助

时间:10-02

整理:3721RD

点击:

spectreVerilog仿真不正常啊!版本5141+mmsim72+ius82

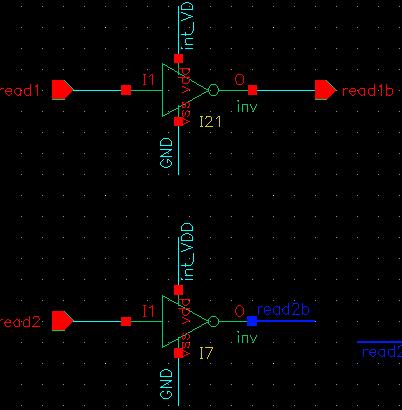

情况是这样的。电路上是两个非门,调用的单元是一样的非门,使用functional的view仿真。

这两个非门在上层的sch里面输入是短接在一起了。因为输入端还在sch里连了mos,所以输入端信号是mix的。

下面那个非门(INV_bottom)输出连了mos,所以是mix的。这个非门输出正常。

上面那个非门(INV_top)不正常。它的输出在sch里连了mos,输出到上层sch里又连了一个非门(用functional view仿真,给它起名INV_ext)。这个非门输出不正常。

查了input.scs的IE model,没有问题啊!

不正常的现象如下:输入大多数时间是0,中间有一个为1的短时间(100uS)脉冲。INV_top的输出一直是0(奇怪啊!)。INV_ext的输出开始是0,当INV_top输入变1时,INV_ext的输出变1;但是当INV_top输入变回0时,INV_ext的输出没变回0来(费解啊!)。

也就是说中间的INV_top输出看不出波形变化来,但是输入的上升沿莫名其妙得传到了输出;更加莫名其妙的是输入的下降沿没有传过去。

我在INV_ext的输入线上串联了一个V=0的电压源,那么一切仿真都是正常的。

有人遇到过同样的问题么?

我的仿真出了什么问题?怎么做能够让仿真正常?

情况是这样的。电路上是两个非门,调用的单元是一样的非门,使用functional的view仿真。

这两个非门在上层的sch里面输入是短接在一起了。因为输入端还在sch里连了mos,所以输入端信号是mix的。

下面那个非门(INV_bottom)输出连了mos,所以是mix的。这个非门输出正常。

上面那个非门(INV_top)不正常。它的输出在sch里连了mos,输出到上层sch里又连了一个非门(用functional view仿真,给它起名INV_ext)。这个非门输出不正常。

查了input.scs的IE model,没有问题啊!

不正常的现象如下:输入大多数时间是0,中间有一个为1的短时间(100uS)脉冲。INV_top的输出一直是0(奇怪啊!)。INV_ext的输出开始是0,当INV_top输入变1时,INV_ext的输出变1;但是当INV_top输入变回0时,INV_ext的输出没变回0来(费解啊!)。

也就是说中间的INV_top输出看不出波形变化来,但是输入的上升沿莫名其妙得传到了输出;更加莫名其妙的是输入的下降沿没有传过去。

我在INV_ext的输入线上串联了一个V=0的电压源,那么一切仿真都是正常的。

有人遇到过同样的问题么?

我的仿真出了什么问题?怎么做能够让仿真正常?

求助求助求助求助

问题还是没有解决,郁闷

如果spectreVerilog仿真器都不可信了,设计还怎么做啊!

不知道啊,帮你顶