关于建立时间的问题

要求5ns建立时间,按照建立精度10e-3算,5ns>7*(1/w),即f>7/5ns/(2*pi)=223MHz。

所以你的带宽指的是f=600MHz的话,建立理论上应该没有问题。

你可以再增大电流或者减小电容试试,感觉这个op有点恐怖。

更完整的建立时间的公式是ts=(Avf/w)*lin(1/e)=7*(avf/w)=5ns,所以GB=w/2/pi=7*Avf/(5ns*2*pi)=Avf*222.9Mhz,注意e为建立精度,Avf为运放测试建立时间时接成的反馈的闭环增益,如果是单位增益形式,则Avf=1,即得楼上计算的结果,所以小编应该检查一下具体应用的时候反馈闭环增益为多少,以上公式见拉查维Design of Analog CMOS Integrated Circuits,英文版p295.

对于给定的负载电容,必须增大运放的电流负载的电流,而要维持同样的最大输出摆幅,所有晶体管必须有较大的栅宽,其结果增大了功耗.因此要在这些方面进行折衷!

说的太好了,学到东西了

谢谢各位兄台!我在测试建立时间的时候是接成跟随形式,即Avf=1,但是应用在两倍增益的残差中,即采样与保持电容的大小是2倍关系!

但是现在感觉增大电流并不能改善我的建立时间,我现在的补偿电容是2P,如果改成1P,的确可以使大信号建立明显变好,但是这样做会严重影响相位鱼肚!我现在就是找不到更好的办法既能降低大信号建立时间有能提高相位鱼肚的办法,请各位不吝赐教!在下谢谢了!

你的设计给课程用,还是给真正设计的?

如果是后者,你必须要用实际的运用情况来测试。

而且看phase margin, 是要看close loop 的情况。 一般都有feedback factor, 减小你的loop bandwidht, 会让phase margin 好的。

跟随形式的情况,一般只有reference buffer, voltage buffer 之类的才有用倒。

MDAC 的amplifier, 可不是source follower configuraiton

如果还有问题,试试加大输出级电流。减小compensation cap. 或者用cascode compensation

谢谢vdslafe!我的是实际应用!我现在就是在闭环下测试的,第一级用的是连续时间共模反馈!

我加大了输出级的电流,但是仍然不行。虽然的确可以改善,但是有限度啊!

请问如何减小loop bandwidht啊?

什么是cascode compensation啊?

谢谢!

实际应用,MDAC amplifier 怎么会是跟随模式? 应该是gain = -2 的voltage amplifier, with feedback factor of 1/3 (如果gate cap 不算).

如果你需要loop bandwidth 600MHz, 你是要设计100Msps 14b?

增大输出电流的时候要减小你的compensation cap 和zero resistor.

你的共模电路能稳定么? 如果你diff loop 都不稳定

我设计的是100M,12bit,我的第一级共模反馈应该是正确的,因为输入变化200mv,输出直流变化只有6mv,

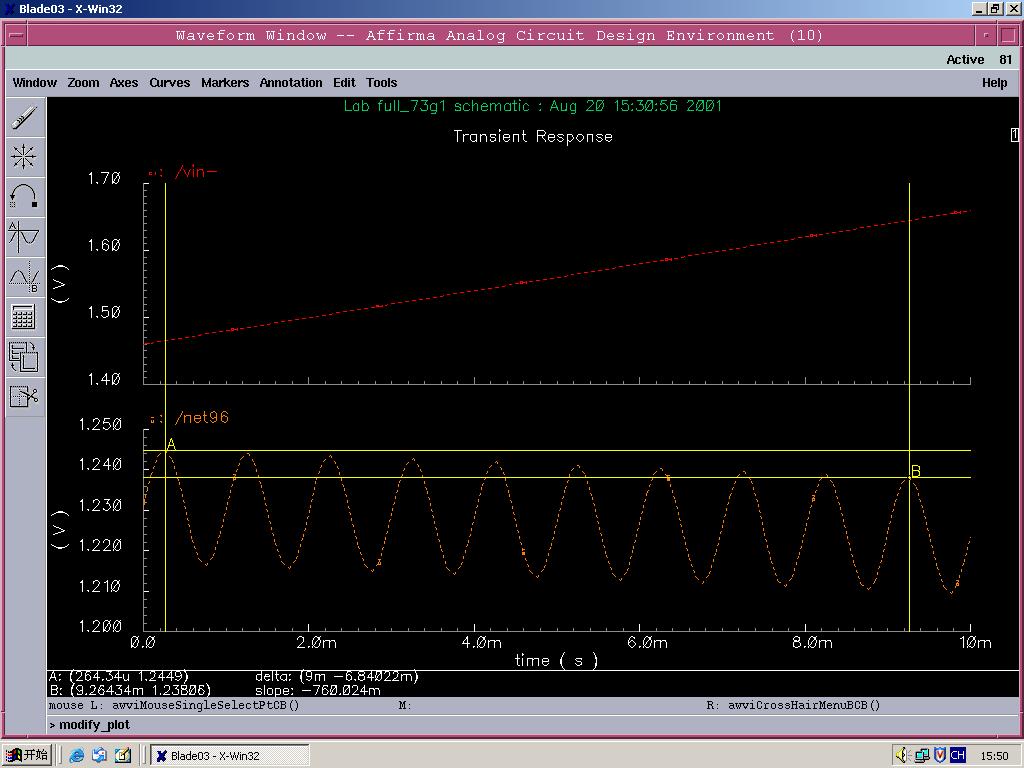

这是测试电路图,你看正确么?

不太对头啊。

为啥你的输出会个正弦波。你还加上差分输入了?

而且频率怎么这么慢? 才1,2k?

我的输入也是正弦波啊!只是幅度太小,看不出来而已,我的输入正弦波0.2V的直流变化正好被抑制了啊!

我测试了一下,输入频率20M的图象最后结果跟上面的一样!

用的测试方法不对

应该用common mode step response.

看有没ring

小编好,你做的是pipeline ADC吗?

我想问的是你是怎么进行建立时间的仿真的呢?

是使用理想模型作反馈环路,还是使用开关电容结构呢?

如果是后者,你的建立时间 是SR 限制较大 还是 step responce 中的 ring所占时间较长呢?

我的第一级用的是连续是CMFB,在测试建立时第二级暂时没有用CMFB,本来我是想用SC CMFB,但是测试建立时感觉用了又不太对。

我的建立主要是SR影响很大,Ring倒是很小,才2ns,我现在就是在想怎样提高SR,都郁闷了一个月了!

你有什么好办法么?

学习。

如果SR所占的比重比较大的话,只有减小负载电容 增大电流两种方法,不过你的电流已经很大了阿!

在余量放大器中是要放大两倍的(一级一位精度),那么 你的600M带宽应该不够 100Msample吧。

我最近也在作pipeline ADC 使用开关电容作反馈网络,理想开关的时候 建立精度 12bit 建立时间 7ns,可是 使用了 实际开关之后 怎么做不到12bit精度了。

神阿 救救我吧!

如果是因为SR太小引起的建立时间太长,应该增大输入级的尾电流吧,不是输出级的电流。SR主要由变化的最大电流决定的,与输出级没什么关系吧,输出级在没信号输入的时候上下电流是匹配的,当有信号输入时,输出级电流的变化实际上就是输入级尾电流啊。

经典的讨论帖

受教啦

SR应该由两级的电流决定,你这个要求确实有点高,加上瞬间的脉冲slew rating的时间应该较长,可以考虑用一级的gain boosting结构

学习了。

经典的讨论帖