-3db频率一直上不去,毕业设计卡住了,版主高手帮帮忙!

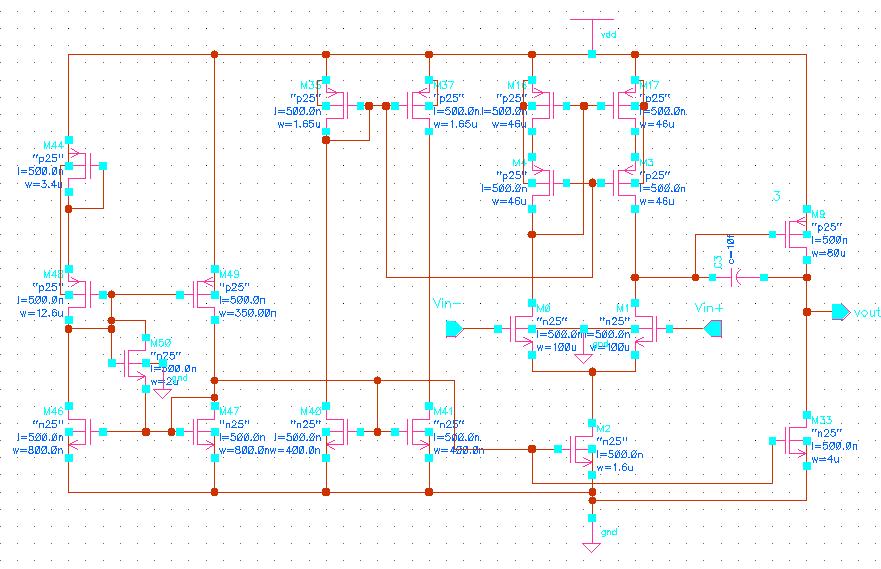

附件是运放电路图,-3db的频率就100k左右,去掉Cc,直接用电阻,顶多也就1M,离50M的目标太遥远了,快毕业不了了,大家帮帮忙吧

没搞错吧,3db频率50M?算你dc增益40db,GBW=5G?你确定你的工艺能做到?

同意2楼的

一般op应该是闭环应用,闭环的-3db带宽与op自身的gbw有关,与op自身的-3db带宽无关

所以,你的参数要求是不是错了阿

当然,如果是比较器,那就另讲了

不过看你的图,有miller补偿

那应该是闭环工作吧

你用什么工艺做的?

如果工艺本身就不能达到,说什么都没有用.

回复 #6 tomjack 的帖子

如果你要-3db带宽越大,就肯定不能用米勒补偿?

另外同意2楼意见.

回复 #2 maplefire 的帖子

同意2楼的,楼猪的运放应该是在闭环使用的吧

怎么高,不现实的

#5楼同学说的不错

你可能定义搞错了

看样子似乎是0.35的双阱工艺,要达到这样的速度不太可能吧。

小编应该是要求GB=50M。

还有负载用cacode太离谱了,而且跨导还那么大,先不谈有没有用,噪声倒是大了不少,是不是设计得有点问题。

的确是哈,输入管子搞那么大,降低1/f噪声?提高增益?可这样做都不是好办法啊。LZ的运放第一级可以用折叠,如果是5V电源的话。nesta说得很有道理

看不到图啊!

回复 #1 rcyang 的帖子

同意2楼的观点。

3dB50M,假设你的单极点,看你电路图的名称应该是85dBDC增益,那单位增益带宽>500G,假设你的弥勒电容只有1p,那输入管跨导就得>0.5,这个cmos工艺不是容易实现的啊!是不是指标要求错了?

应该是有些参数要求搞错了

这里牛人多啊

工艺

比较同意上面的看法,关键看你的工艺,有的工艺上数字,50M没有问题,

但模拟不行。

50M肯定是指接成闭环应用时的带宽,一般都这样的定义。如果是接成单位增益应用的话,在你说的-3dB带宽有100K(应该是开环看的吧,而且没有补偿稳定吧)时,增益有50时,GBW就有50M了。 这个简单的2级的运放应该是做得到的。

zan 5lou de

如果用casdode,输入对管也应该是把,不然跟没用一样...

这种结构的除非应用在反馈中才有可能达到如此带宽

要確認你的工艺是否能達到這麼大的GBW=5G.

加反馈

初学者,看都看不懂哦

高手多阿,我也以为反馈下应用比较实际。

晕死!-3db 要那么高,性能就太好了!应该是GB吧!

可以做到

可以 做的到的在第一放大的输出端用shunt反馈

allen书上有的第381页给出了示意图

你要是急着要用的话建议最好找consolid-statecircuits那上面多的是这样的例子

查找80--90年的可能比较多90--2000年的比较少

做出来的放大倍数比较小也就是10来倍

要多看书啊!

等大家的讨论结果……

真要想达到50MHz的带宽,看来只能用单级放大器,或者第一级怎一很小的那种放大器了。

而且即使这样,很有可能受到工艺的限制,依然达不到50M

估计只有把第一级增益降下来才能得到那么高的-3db带宽

50M?

50MHz有些问题,不过你可以考虑提高second stage ,采用load compensated cascode amplifier. 这样对提高增益有较大的作用。